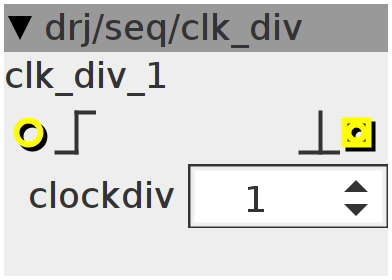

clk_div

Clock divider

IO Variants: 2

Variant: 1

Inlets

bool32.rising Clock input

Outlets

bool32.pulse Clock output

Parameters

int32 clockdiv

uint32_t clock_count;

uint32_t old_clk;clock_count = 0;

old_clk = 0;outlet_clk = 0;

if (inlet_clk && !old_clk) {

clock_count++;

if (clock_count >= param_clockdiv) {

clock_count = 0;

outlet_clk = 1;

}

}

old_clk = inlet_clk;Variant: 2

Inlets

bool32.rising Clock input

bool32.rising Reset input

Outlets

bool32.pulse Clock output

Parameters

int32 clockdiv

uint32_t clock_count;

uint32_t old_clk;

uint32_t old_r;clock_count = 0;

old_clk = 0;

old_r = 0;outlet_clk = 0;

if (inlet_r && !old_r) {

clock_count = 0;

} else if (inlet_clk && !old_clk) {

clock_count++;

if (clock_count >= param_clockdiv) {

clock_count = 0;

outlet_clk = 1;

}

}

old_clk = inlet_clk;

old_r = inlet_r;