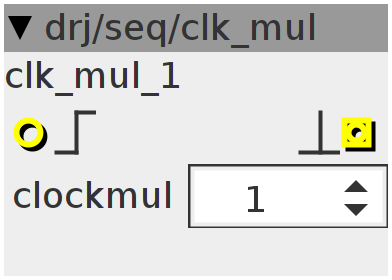

clk_mul

Clock multiplier

Inlets

bool32.rising Clock input

Outlets

bool32.pulse Clock output

Parameters

int32 clockmul

Declaration

uint32_t synced;

uint32_t ktimer;

uint32_t last_ktime;

uint32_t period;

uint32_t last_period;

uint32_t remaining_clocks;

uint32_t old_clk;

Init

synced = 0;

ktimer = 0;

last_ktime = ktimer;

period = 1;

last_period = period;

remaining_clocks = 0;

old_clk = 0;

Control Rate

outlet_clk = 0;

if (inlet_clk && !old_clk) {

float tmp_period = (ktimer - last_ktime);

period = (int32_t)((tmp_period / param_clockmul) + 0.5f);

if (period < 2) {

period = 2;

}

last_ktime = ktimer;

last_period = period;

remaining_clocks = param_clockmul - 1;

if (synced < 2) {

synced++;

} else {

outlet_clk = 1;

}

} else if (synced >= 2 && remaining_clocks > 0 && --period == 0) {

remaining_clocks--;

period = last_period;

outlet_clk = 1;

}

old_clk = inlet_clk;

ktimer++;