stepseq_8_switch

Step sequencer, switch x 8

IO Variants: 3

Variant: 1

Inlets

int32 Step select input

frac32 Signal 1 input

frac32 Signal 2 input

frac32 Signal 3 input

bool32 Gate 1 input

Outlets

int32 Chain step output

bool32 Switch output

bool32 Gate 1 output

frac32 Signal 1 output

frac32 Signal 2 output

frac32 Signal 3 output

Parameters

bool32.tgl s1

bool32.tgl s2

bool32.tgl s3

bool32.tgl s4

bool32.tgl s5

bool32.tgl s6

bool32.tgl s7

bool32.tgl s8

switch (inlet_step) {

case 0:

outlet_out = param_s1;

break;

case 1:

outlet_out = param_s2;

break;

case 2:

outlet_out = param_s3;

break;

case 3:

outlet_out = param_s4;

break;

case 4:

outlet_out = param_s5;

break;

case 5:

outlet_out = param_s6;

break;

case 6:

outlet_out = param_s7;

break;

case 7:

outlet_out = param_s8;

break;

default:

outlet_out = 0;

break;

}

if (outlet_out) {

outlet_sig1 = inlet_sig1;

outlet_sig2 = inlet_sig2;

outlet_sig3 = inlet_sig3;

outlet_gate1 = inlet_gate1;

} else {

outlet_sig1 = 0;

outlet_sig2 = 0;

outlet_sig3 = 0;

outlet_gate1 = 0;

}

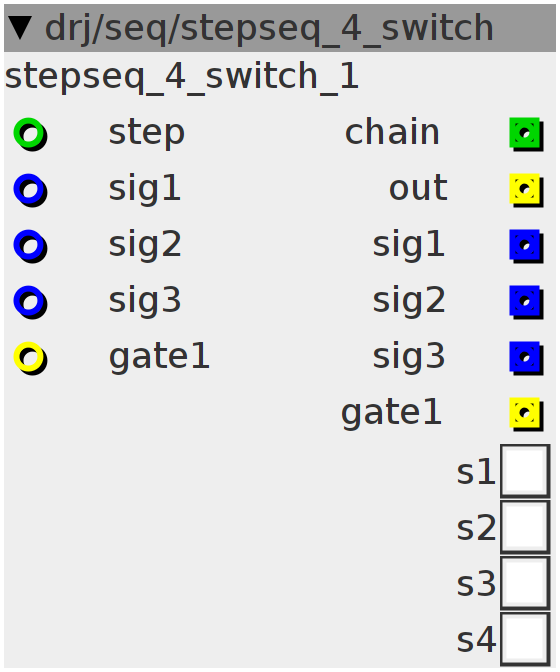

outlet_chain = inlet_step - 8;Variant: 2

Inlets

int32 Step select input

frac32 Signal 1 input

frac32 Signal 2 input

frac32 Signal 3 input

bool32 Gate 1 input

Outlets

int32 Chain step output

bool32 Switch output

bool32 Gate 1 output

frac32 Signal 1 output

frac32 Signal 2 output

frac32 Signal 3 output

Parameters

bool32.tgl s1

bool32.tgl s2

bool32.tgl s3

bool32.tgl s4

switch (inlet_step) {

case 0:

outlet_out = param_s1;

break;

case 1:

outlet_out = param_s2;

break;

case 2:

outlet_out = param_s3;

break;

case 3:

outlet_out = param_s4;

break;

default:

outlet_out = 0;

break;

}

if (outlet_out) {

outlet_sig1 = inlet_sig1;

outlet_sig2 = inlet_sig2;

outlet_sig3 = inlet_sig3;

outlet_gate1 = inlet_gate1;

} else {

outlet_sig1 = 0;

outlet_sig2 = 0;

outlet_sig3 = 0;

outlet_gate1 = 0;

}

outlet_chain = inlet_step - 4;Variant: 3

Inlets

frac32 Signal 1 input

frac32 Signal 2 input

frac32 Signal 3 input

bool32 Gate 1 input

int32 Step select input

Outlets

bool32 Switch output

bool32 Gate 1 output

frac32 Signal 1 output

frac32 Signal 2 output

frac32 Signal 3 output

int32 Chain step output

Parameters

bool32.tgl s1

bool32.tgl s2

bool32.tgl s3

bool32.tgl s4

bool32.tgl s5

bool32.tgl s6

bool32.tgl s7

bool32.tgl s8

bool32.tgl s9

bool32.tgl s10

bool32.tgl s11

bool32.tgl s12

bool32.tgl s13

bool32.tgl s14

bool32.tgl s15

bool32.tgl s16

switch (inlet_step) {

case 0:

outlet_out = param_s1;

break;

case 1:

outlet_out = param_s2;

break;

case 2:

outlet_out = param_s3;

break;

case 3:

outlet_out = param_s4;

break;

case 4:

outlet_out = param_s5;

break;

case 5:

outlet_out = param_s6;

break;

case 6:

outlet_out = param_s7;

break;

case 7:

outlet_out = param_s8;

break;

case 8:

outlet_out = param_s9;

break;

case 9:

outlet_out = param_s10;

break;

case 10:

outlet_out = param_s11;

break;

case 11:

outlet_out = param_s12;

break;

case 12:

outlet_out = param_s13;

break;

case 13:

outlet_out = param_s14;

break;

case 14:

outlet_out = param_s15;

break;

case 15:

outlet_out = param_s16;

break;

default:

outlet_out = 0;

break;

}

if (outlet_out) {

outlet_sig1 = inlet_sig1;

outlet_sig2 = inlet_sig2;

outlet_sig3 = inlet_sig3;

outlet_gate1 = inlet_gate1;

} else {

outlet_sig1 = 0;

outlet_sig2 = 0;

outlet_sig3 = 0;

outlet_gate1 = 0;

}

outlet_chain = inlet_step - 16;