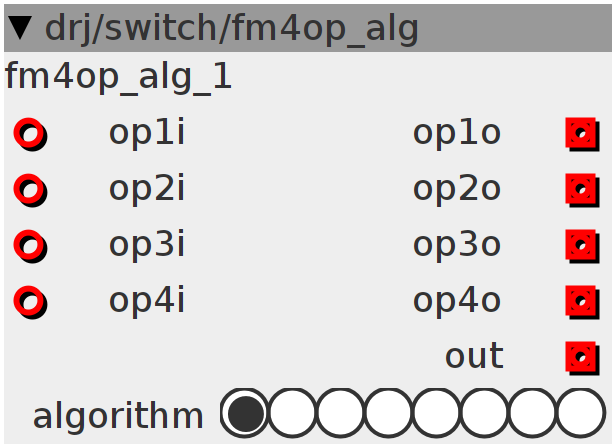

fm4op_alg

FM 4 op algorithm router ala TX81Z, but with a feedback path on all leaf operators

Inlets

frac32buffer Op 1 input

frac32buffer OP 2 input

frac32buffer OP 3 input

frac32buffer OP 4 input

Outlets

frac32buffer Op 1 output

frac32buffer Op 2 output

frac32buffer Op 3 output

frac32buffer Op 4 output

frac32buffer Output

Parameters

int32.hradio algorithm

int32_t j;

/*

* TX81Z algorithms:

* 1: op4 -> op3 -> op2 -> op1

* 2: (op4 + op3) -> op2 -> op1

* 3: op3 -> op2 + op4 -> op1

* 4: op4 -> op3 + op2 -> op1

* 5: (op2 -> op1) + (op4 -> op3)

* 6: (op4 -> op1) + (op4 -> op2) + op4 -> op3)

* 7: op1 + op2 + (op4 -> op3)

* 8: op1 + op2 + op3 + op4

*/

switch (param_algorithm) {

case 0:

// 1: op4 -> op3 -> op2 -> op1

for (j = 0; j < BUFSIZE; ++j) {

outlet_op1o[j] = inlet_op2i[j];

outlet_op2o[j] = inlet_op3i[j];

outlet_op3o[j] = inlet_op4i[j];

outlet_op4o[j] = inlet_op4i[j];

outlet_out[j] = __SSAT(inlet_op1i[j], 28);

}

break;

case 1:

// 2: (op4 + op3) -> op2 -> op1

for (j = 0; j < BUFSIZE; ++j) {

outlet_op1o[j] = inlet_op2i[j];

outlet_op2o[j] = inlet_op3i[j] + inlet_op4i[j];

outlet_op3o[j] = inlet_op3i[j]; // = 0

outlet_op4o[j] = inlet_op4i[j];

outlet_out[j] = __SSAT(inlet_op1i[j], 28);

}

break;

case 2:

// 3: op3 -> op2 + op4 -> op1

for (j = 0; j < BUFSIZE; ++j) {

outlet_op1o[j] = inlet_op2i[j] + inlet_op4i[j];

outlet_op2o[j] = inlet_op3i[j];

outlet_op3o[j] = inlet_op3i[j]; // = 0

outlet_op4o[j] = inlet_op4i[j];

outlet_out[j] = __SSAT(inlet_op1i[j], 28);

}

break;

case 3:

// 4: op4 -> op3 + op2 -> op1

for (j = 0; j < BUFSIZE; ++j) {

outlet_op1o[j] = inlet_op2i[j] + inlet_op3i[j];

outlet_op2o[j] = inlet_op2i[j]; // = 0;

outlet_op3o[j] = inlet_op4i[j];

outlet_op4o[j] = inlet_op4i[j];

outlet_out[j] = __SSAT(inlet_op1i[j], 28);

}

break;

case 4:

// 5: (op2 -> op1) + (op4 -> op3)

for (j = 0; j < BUFSIZE; ++j) {

outlet_op1o[j] = inlet_op2i[j];

outlet_op2o[j] = inlet_op2i[j]; // = 0;

outlet_op3o[j] = inlet_op4i[j];

outlet_op4o[j] = inlet_op4i[j];

outlet_out[j] = __SSAT(inlet_op1i[j] + inlet_op3i[j], 28);

}

break;

case 5:

// 6: (op4 -> op1) + (op4 -> op2) + (op4 -> op3)

for (j = 0; j < BUFSIZE; ++j) {

outlet_op1o[j] = inlet_op4i[j];

outlet_op2o[j] = inlet_op4i[j];

outlet_op3o[j] = inlet_op4i[j];

outlet_op4o[j] = inlet_op4i[j];

outlet_out[j] = __SSAT(inlet_op1i[j] + inlet_op2i[j] + inlet_op3i[j], 28);

}

break;

case 6:

// 7: op1 + op2 + (op4 -> op3)

for (j = 0; j < BUFSIZE; ++j) {

outlet_op1o[j] = inlet_op1i[j]; //= 0;

outlet_op2o[j] = inlet_op2i[j]; //= 0;

outlet_op3o[j] = inlet_op4i[j];

outlet_op4o[j] = inlet_op4i[j];

outlet_out[j] = __SSAT(inlet_op1i[j] + inlet_op2i[j] + inlet_op3i[j], 28);

}

break;

case 7:

// 8: op1 + op2 + op3 + op4

for (j = 0; j < BUFSIZE; ++j) {

outlet_op1o[j] = inlet_op1i[j]; // = 0

outlet_op2o[j] = inlet_op2i[j]; // = 0

outlet_op3o[j] = inlet_op3i[j]; // = 0

outlet_op4o[j] = inlet_op4i[j];

outlet_out[j] = __SSAT(

inlet_op1i[j] + inlet_op2i[j] + inlet_op3i[j] + inlet_op4i[j], 28);

}

break;

}