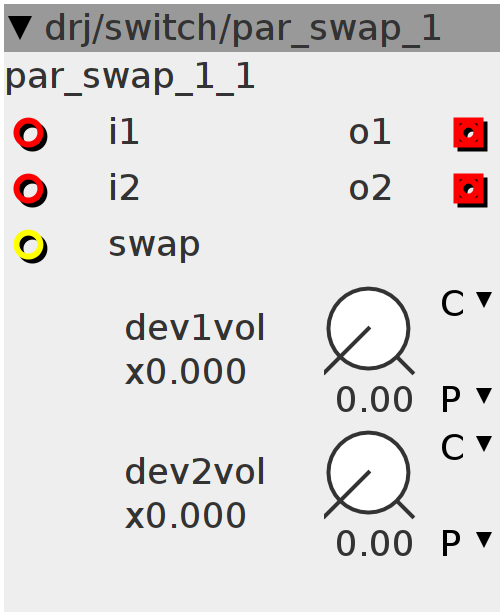

par_swap_2

Stereo swappable parallel routing switch

IO Variants: 2

Variant: 1

Inlets

bool32 Swap device 1 and 2 outputs

frac32buffer Input 1 L

frac32buffer Input 1 R

frac32buffer Input 2 L

frac32buffer Input 2 R

Outlets

frac32buffer Output 1 L

frac32buffer Output 1 R

frac32buffer Output 2 L

frac32buffer Output 2 R

Parameters

frac32.u.map.squaregain Device 1 volume

frac32.u.map.squaregain Device 2 volume

int32_t j, outl, outr;

if (inlet_swap) {

for (j = 0; j < BUFSIZE; ++j) {

// Feed input 1 to out 2

// Feed input 2 to out 1

outlet_o1l[j] = ___SMMUL(inlet_i2l[j] << 3, param_dev2vol << 2);

outlet_o1r[j] = ___SMMUL(inlet_i2r[j] << 3, param_dev2vol << 2);

outlet_o2l[j] = ___SMMUL(inlet_i1l[j] << 3, param_dev1vol << 2);

outlet_o2r[j] = ___SMMUL(inlet_i1r[j] << 3, param_dev1vol << 2);

}

} else {

for (j = 0; j < BUFSIZE; ++j) {

// Feed input 1 to out 1

// Feed input 2 to out 2

outlet_o1l[j] = ___SMMUL(inlet_i1l[j] << 3, param_dev1vol << 2);

outlet_o1r[j] = ___SMMUL(inlet_i1r[j] << 3, param_dev1vol << 2);

outlet_o2l[j] = ___SMMUL(inlet_i2l[j] << 3, param_dev2vol << 2);

outlet_o2r[j] = ___SMMUL(inlet_i2r[j] << 3, param_dev2vol << 2);

}

}Variant: 2

Inlets

frac32buffer Input 1

frac32buffer Input 2

bool32 Swap device 1 and 2 outputs

Outlets

frac32buffer Output 1

frac32buffer Output 2

Parameters

frac32.u.map.squaregain Device 1 volume

frac32.u.map.squaregain Device 2 volume

int32_t j, out;

if (inlet_swap) {

for (j = 0; j < BUFSIZE; ++j) {

// Feed input 1 to out 2

// Feed input 2 to out 1

outlet_o2[j] = ___SMMUL(inlet_i1[j] << 3, param_dev1vol << 2);

outlet_o1[j] = ___SMMUL(inlet_i2[j] << 3, param_dev2vol << 2);

}

} else {

for (j = 0; j < BUFSIZE; ++j) {

// Feed input 1 to out 1

// Feed input 2 to out 2

outlet_o1[j] = ___SMMUL(inlet_i1[j] << 3, param_dev1vol << 2);

outlet_o2[j] = ___SMMUL(inlet_i2[j] << 3, param_dev2vol << 2);

}

}