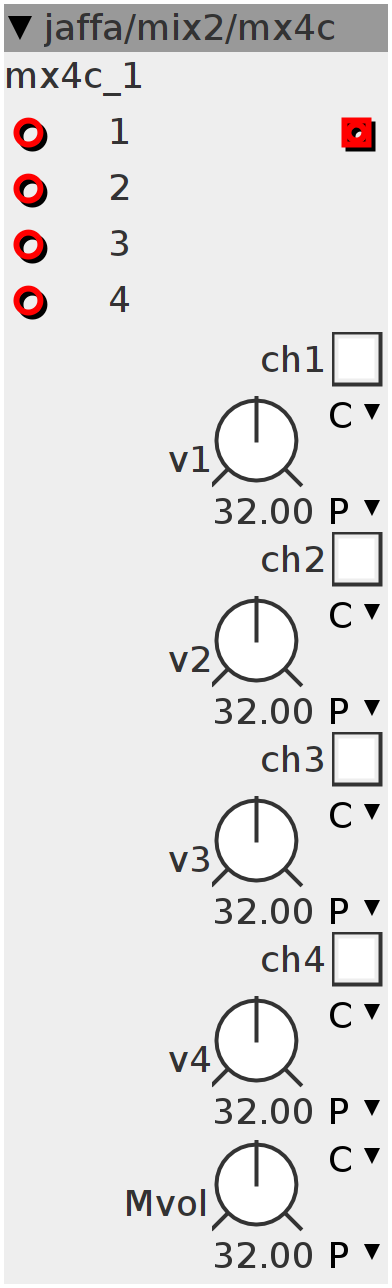

mx4c

4 channel mixer. 3% DSP

Inlets

frac32buffer 1

frac32buffer 2

frac32buffer 3

frac32buffer 4

Outlets

frac32buffer Master out L

Parameters

bool32.tgl ch1

bool32.tgl ch2

bool32.tgl ch3

bool32.tgl ch4

frac32.u.map Ch1. volume

frac32.u.map Ch2. volume

frac32.u.map Ch3. volume

frac32.u.map Ch4. volume

frac32.u.map Master volume

// Channel 1 //

int32_t CHANNELONE;

if (param_ch1 > 0) {

CHANNELONE = ___SMMUL(inlet_1 << 3, param_v1 << 2);

} else {

CHANNELONE = 0;

}

// Channel 1 route //

int32_t CH1MAIN = (param_ch1 == 1) ? CHANNELONE : 0;

// Channel 2 //

int32_t CHANNELTWO;

if (param_ch2 > 0) {

CHANNELTWO = ___SMMUL(inlet_2 << 3, param_v2 << 2);

} else {

CHANNELTWO = 0;

}

// Channel 2 route //

int32_t CH2MAIN = (param_ch2 == 1) ? CHANNELTWO : 0;

// Channel 3 //

int32_t CHANNELTHREE;

if (param_ch3 > 0) {

CHANNELTHREE = ___SMMUL(inlet_3 << 3, param_v3 << 2);

} else {

CHANNELTHREE = 0;

}

// Channel 3 route //

int32_t CH3MAIN = (param_ch3 == 1) ? CHANNELTHREE : 0;

// Channel 4 //

int32_t CHANNELFOUR;

if (param_ch4 > 0) {

CHANNELFOUR = ___SMMUL(inlet_4 << 3, param_v4 << 2);

} else {

CHANNELFOUR = 0;

}

// Channel 4 route //

int32_t CH4MAIN = (param_ch4 == 1) ? CHANNELFOUR : 0;

// Final master out volume on outlet_m before going to master effect //

outlet_m =

___SMMUL((CH1MAIN + CH2MAIN + CH3MAIN + CH4MAIN) << 3, param_Mvol << 2);