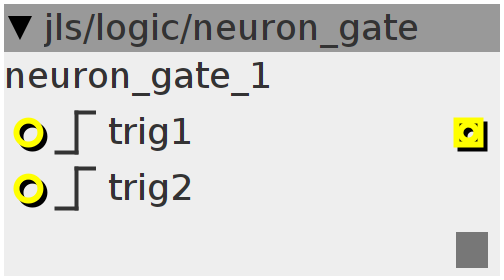

neuron_gate

Simple Neural-Net Gate

Inlets

bool32.rising trigger 1

bool32.rising trigger 2

Outlets

bool32 gate

Displays

bool32 gate

Declaration

int ntrig;

bool tmp;

int X[1][2];

float W1[2][3];

float W2[3][1];

float Wo1[1][3];

float sum;

float Y;

float sigmoid(float x) { return 1 / (1 + abs(x)); }

int round_int(float r) { return (r > 0.0) ? (r + 0.5) : (r - 0.5); }

Init

ntrig = 0;

tmp = 0;

X[0][0] = 1;

X[0][1] = 0;

W1[0][0] = 0.74000854;

W1[0][1] = 4.47769531;

W1[0][2] = -0.98692059;

W1[1][0] = 0.83034991;

W1[1][1] = 4.48772758;

W1[1][2] = -0.55733578;

W2[0][0] = -6.17234487;

W2[1][0] = 4.8835918;

W2[2][0] = 1.28875386;

sum = 0;

Y = 0;

Control Rate

if ((inlet_trig1 > 0) || (inlet_trig2 > 0) && !ntrig) {

ntrig = 1;

X[0][0] = inlet_trig1;

X[0][1] = inlet_trig2;

for (int i = 0; i < 1; i++) {

for (int j = 0; j < 3; j++) {

for (int k = 0; k < 2; k++) {

sum += X[i][k] * W1[k][j];

}

Wo1[i][j] = sigmoid(sum);

sum = 0;

}

}

for (int i = 0; i < 1; i++) {

for (int j = 0; j < 1; j++) {

for (int k = 0; k < 3; k++) {

Y += Wo1[i][k] * W2[k][j];

}

}

}

Y = round_int(Y);

tmp = Y;

Y = 0;

} else if (!((inlet_trig1 > 0) || (inlet_trig2 > 0)))

ntrig = 0;

outlet_gate = tmp;

disp_gate = tmp;