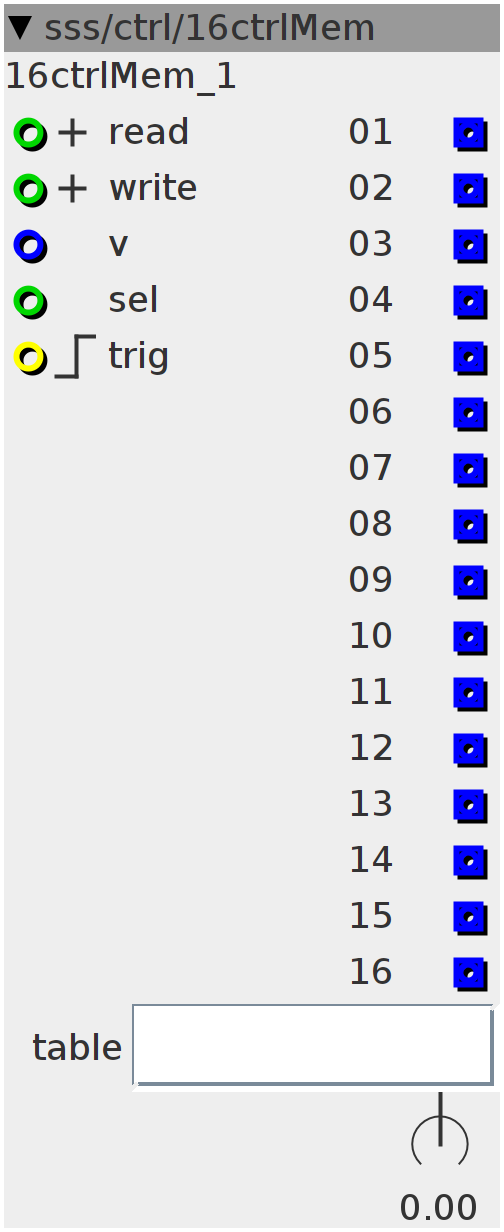

16ctrlMem

16 output modulation recorder

Inlets

bool32.rising save value into table position

int32.positive internal preset read position within the table

int32.positive internal preset write position within the table

frac32 v

int32 select parameter 1 to 16 to write to

Outlets

frac32 01

frac32 02

frac32 03

frac32 04

frac32 05

frac32 06

frac32 07

frac32 08

frac32 09

frac32 10

frac32 11

frac32 12

frac32 13

frac32 14

frac32 15

frac32 16

Attributes

objref table

Displays

frac32.s.dial sel

// nothing to change here when you're editting

int ntrig;// nothing to change here when you're editting

ntrig = 0;// when adding outputs, also add cases. Also adjust:

// write offset (2 instances per case!)

// inlet_write multiplier (next line) maximum offset+1)

int32_t write = inlet_write * 16;

switch (inlet_sel > 0 ? inlet_sel : 0) {

case 0:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (write < attr_table.LENGTH)

attr_table.array[write] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 1:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 1) < attr_table.LENGTH)

attr_table.array[write + 1] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 2:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 2) < attr_table.LENGTH)

attr_table.array[write + 2] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 3:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 3) < attr_table.LENGTH)

attr_table.array[write + 3] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 4:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 4) < attr_table.LENGTH)

attr_table.array[write + 4] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 5:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 5) < attr_table.LENGTH)

attr_table.array[write + 5] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 6:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 6) < attr_table.LENGTH)

attr_table.array[write + 6] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 7:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 7) < attr_table.LENGTH)

attr_table.array[write + 7] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 8:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 8) < attr_table.LENGTH)

attr_table.array[write + 8] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 9:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 9) < attr_table.LENGTH)

attr_table.array[write + 9] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 10:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 10) < attr_table.LENGTH)

attr_table.array[write + 10] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 11:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 11) < attr_table.LENGTH)

attr_table.array[write + 11] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 12:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 12) < attr_table.LENGTH)

attr_table.array[write + 12] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 13:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 13) < attr_table.LENGTH)

attr_table.array[write + 13] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 14:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 14) < attr_table.LENGTH)

attr_table.array[write + 14] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 15:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if ((write + 15) < attr_table.LENGTH)

attr_table.array[write + 15] = __SSAT(inlet_v, 28) >> attr_table.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

default:

break;

}

// when adding outputs, also copy more of these lines and adjust

// outlet number

// read offset

// inlet_read multiplier (next line) maximum offset+1)

int32_t read = inlet_read * 16;

outlet_01 = attr_table.array[__USAT(read, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_02 = attr_table.array[__USAT(read + 1, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_03 = attr_table.array[__USAT(read + 2, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_04 = attr_table.array[__USAT(read + 3, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_05 = attr_table.array[__USAT(read + 4, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_06 = attr_table.array[__USAT(read + 5, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_07 = attr_table.array[__USAT(read + 6, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_08 = attr_table.array[__USAT(read + 7, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_09 = attr_table.array[__USAT(read + 8, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_10 = attr_table.array[__USAT(read + 9, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_11 = attr_table.array[__USAT(read + 10, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_12 = attr_table.array[__USAT(read + 11, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_13 = attr_table.array[__USAT(read + 12, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_14 = attr_table.array[__USAT(read + 13, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_15 = attr_table.array[__USAT(read + 14, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

outlet_16 = attr_table.array[__USAT(read + 15, attr_table.LENGTHPOW)]

<< attr_table.GAIN;

// when adding outputs, also add cases. respective output send to disp_sel

switch (inlet_sel > 0 ? inlet_sel : 0) {

case 0:

disp_sel = outlet_01;

break;

case 1:

disp_sel = outlet_02;

break;

case 2:

disp_sel = outlet_03;

break;

case 3:

disp_sel = outlet_04;

break;

case 4:

disp_sel = outlet_05;

break;

case 5:

disp_sel = outlet_06;

break;

case 6:

disp_sel = outlet_07;

break;

case 7:

disp_sel = outlet_08;

break;

case 8:

disp_sel = outlet_09;

break;

case 9:

disp_sel = outlet_10;

break;

case 10:

disp_sel = outlet_11;

break;

case 11:

disp_sel = outlet_12;

break;

case 12:

disp_sel = outlet_13;

break;

case 13:

disp_sel = outlet_14;

break;

case 14:

disp_sel = outlet_15;

break;

case 15:

disp_sel = outlet_16;

break;

}