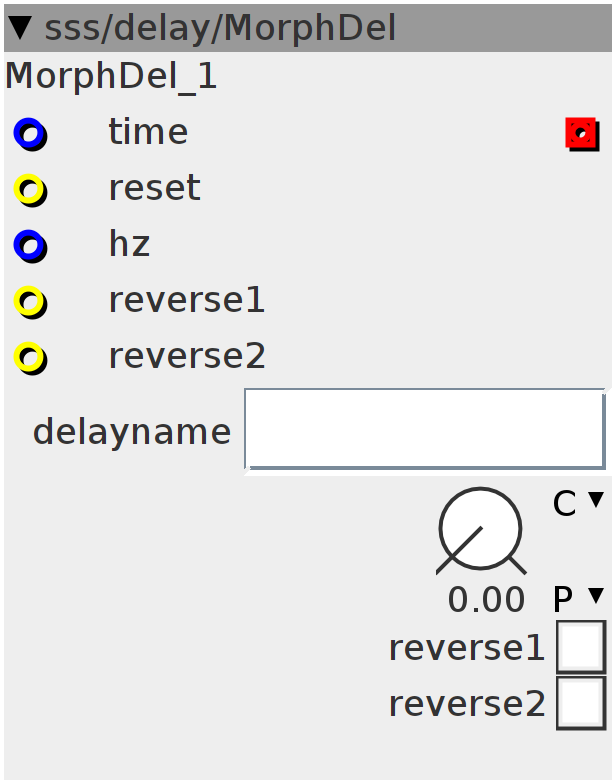

MorphDel

morphing delay, mixing between two readout-taps, which are updated when they are "not in the mix". "hz" input responds to the "clock2timing" module for host-tempo-syncing of the internal mod LFO "time" input resonds to the "clock2timing" module for host-tempo-syncing of delaytime "reset" input smoothly fades the internal LFO to 0 phase in respect to the sampled phase-offset at the time of incoming clock-triggers.

Inlets

frac32 delay time (fraction of total delayline size)

frac32 hz

bool32 reset

bool32 reverse1

bool32 reverse2

Outlets

frac32buffer wave

Parameters

bool32.tgl reverse1

bool32.tgl reverse2

frac32.u.map hz

Attributes

objref delayname

uint32_t Phase;

uint32_t r;

uint32_t h;

int trg1;

int trg2;

int trg3;

int trg4;

int32_t smooth;

int32_t pos1;

int32_t pos2;

uint32_t mem;

uint32_t val;

int8_t reverse1;

int8_t reverse2;Phase = 0;

r = 1;int32_t wave;

if (inlet_reset && r) {

mem = Phase - val;

r = 0;

} else {

if (!inlet_reset)

r = 1;

Phase += ___SMMUL((param_hz + inlet_hz) << 4, ((1 << 31) / 375 * 16));

}

val = val + ((mem - val) >> 8);

wave = ((Phase - val) >> 5);

trg1 = (wave > (1 << 26)) ? (1 << 27) : 0;

trg2 = (1 << 27) - trg1;

int trgA = trg1 * ((trg3 == 0) ? 1 : 0);

int trgB = trg2 * ((trg4 == 0) ? 1 : 0);

trg3 = trg1;

trg4 = trg2;

int32_t Sin;

SINE2TINTERP(Phase - val - (1 << 29), Sin)

int32_t sine = -(Sin >> 3) + (1 << 26);

if (trgA) {

pos1 = inlet_time;

}

if (trgB) {

pos2 = inlet_time;

}

reverse1 = (param_reverse1 + inlet_reverse1) > 0 ? -1 : 1;

reverse2 = (param_reverse2 + inlet_reverse2) > 0 ? -1 : 1;

uint32_t delay1 =

(attr_delayname.writepos -

(__USAT(pos1, 27) >> (27 - attr_delayname.LENGTHPOW)) - BUFSIZE);

uint32_t delay2 =

(attr_delayname.writepos -

(__USAT(pos2, 27) >> (27 - attr_delayname.LENGTHPOW)) - BUFSIZE);smooth = smooth + ((sine - smooth) >> 6);

int32_t sane;

sane = smooth > 0 ? smooth : 0;

sane = sane > (1 << 27) ? (1 << 27) : sane;

outlet_out =

___SMMUL(

attr_delayname.array[(param_reverse2 << 27) + (delay1++) * reverse1 &

attr_delayname.LENGTHMASK]

<< 17,

((1 << 27) - sane) << 2) +

___SMMUL(

attr_delayname.array[(param_reverse2 << 27) + (delay2++) * reverse2 &

attr_delayname.LENGTHMASK]

<< 17,

sane << 2);