IamSin

adds a signal of 2 together amplitude modulated sines, of which the phase is controlled by the incoming signal, to the incoming signal. -the position knobs offset the center (zero) of the modulation by the incoming signal -the width controls control the amplitude of the phase-control for the generated sines -the mod controls control a frequency shift of the phase-control for the generated sines

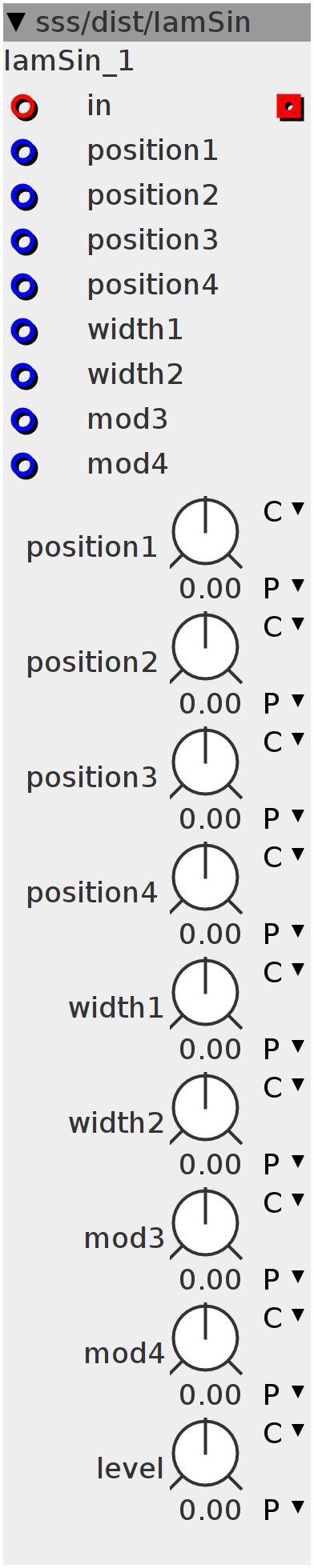

Inlets

frac32buffer in

frac32 position1

frac32 position2

frac32 position3

frac32 position4

frac32 width1

frac32 width2

frac32 mod3

frac32 mod4

Outlets

frac32buffer out

Parameters

frac32.s.map position1

frac32.s.map position2

frac32.s.map position3

frac32.s.map position4

frac32.s.map width1

frac32.s.map width2

frac32.s.map mod3

frac32.s.map mod4

frac32.s.map level

int32_t Position1;

int32_t Position2;

int32_t Position3;

int32_t Position4;

int32_t Mod3;

int32_t Mod4;

int32_t Width1;

int32_t Width2;int32_t POsition1 = param_position1 + inlet_position1;

int32_t POsition2 = param_position2 + inlet_position2;

int32_t POsition3 = param_position3 + inlet_position3;

int32_t POsition4 = param_position4 + inlet_position4;

int32_t width1 = param_width1 + inlet_width1;

int32_t width2 = param_width2 + inlet_width2;

int32_t mod3 = param_mod3 + inlet_mod3;

int32_t mod4 = param_mod4 + inlet_mod4;Position1 += ((POsition1 - Position1) >> 8);

Position2 += ((POsition2 - Position2) >> 8);

Position3 += ((POsition3 - Position3) >> 8);

Position4 += ((POsition4 - Position4) >> 8);

Width1 = Width1 + ((width1 - Width1) >> 8);

Width2 = Width2 + ((width2 - Width2) >> 8);

Mod3 = Mod3 + ((mod3 - Mod3) >> 8);

Mod4 = Mod4 + ((mod4 - Mod4) >> 8);

int32_t in = __SSAT(inlet_in, 27);

int32_t position1a = in - Position1;

int32_t position2 = in - Position2;

int32_t position1b =

position1a + ___SMMUL((position2 - Position3) << 2, Mod3 << 2);

position2 += ___SMMUL((position1a - Position4) << 2, Mod4 << 2);

int32_t sine1;

int32_t sine2;

SINE2TINTERP(___SMMUL(position1b << 3, Width1 << 4) << 4, sine1)

SINE2TINTERP(___SMMUL(position2 << 3, Width2 << 4) << 4, sine2)

outlet_out = ___SMMUL(___SMMUL(sine1 >> 3, sine2 >> 2) << 3, param_level << 2) +

inlet_in;