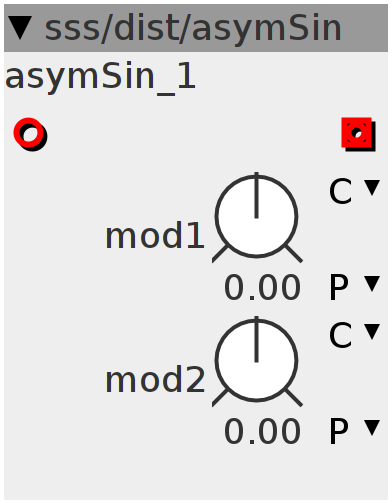

asymSin

Inlets

frac32buffer in

Outlets

frac32buffer out

Parameters

frac32.s.map mod1

frac32.s.map mod2

Declaration

int32_t O1;

Init

SINE2TINTERP(1 << 30, O1)

Control Rate

int32_t mod1 = param_mod1 + 1;

int32_t mod2 = mod1 < 0 ? -mod1 : 0;

mod1 = mod1 > 0 ? mod1 : 0;

int32_t mod3 = param_mod2 + 1;

int32_t mod4 = mod3 < 0 ? -mod3 : 0;

mod3 = mod3 > 0 ? mod3 : 0;

Audio Rate

int32_t in = inlet_in;

if (in > 0) {

in += ___SMMUL(mod2 << 4, in << 4);

} else {

in += ___SMMUL(mod4 << 4, in << 4);

}

int32_t clip = in > mod1 ? mod1 : in;

clip = clip < -mod3 ? -mod3 : clip;

int32_t over = in - clip;

if (over > 0) {

SINE2TINTERP((-over << 4) + (1 << 30), over)

over = over >> 5;

over -= (O1 >> 5);

} else {

SINE2TINTERP((-over << 4) - (1 << 30), over)

over = over >> 5;

over += (O1 >> 5);

}

outlet_out = clip + (over);