CY1

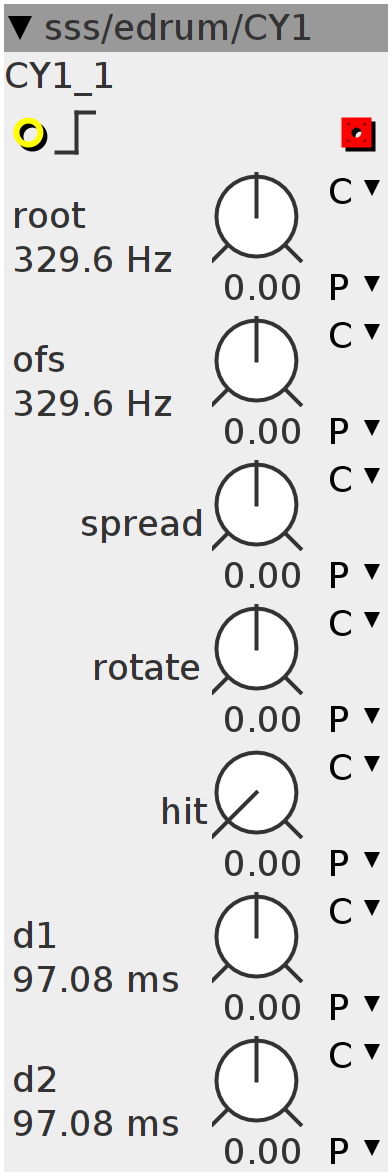

ROOT sets the base frequency from where the pitch offsets are calculated OFS sets a frequency offset to the root pitch, functioning as a frequency shifter (remember Bode?). SPREAD sets an extra offset for each next oscillator pitch (harmonic spreading). ROTATE shifts the frequencies around, following a sine pattern. Stepsize is set by primes. HIT sets attack rate D1 sets start part of the decay rate (short, spikey hits or more "Boings") D2 sets the end part of the decay rate as the decay reaches zero. Use this to shorten the sound or lengthen it (also depends on D1, which can force the decay down pretty easily)

Inlets

bool32.rising gate

Outlets

frac32buffer out

Parameters

frac32.s.map.pitch root

frac32.s.map.pitch ofs

frac32.s.map spread

frac32.s.map rotate

frac32.u.map hit

frac32.s.map.kdecaytime.exp d1

frac32.s.map.kdecaytime.exp d2

uint32_t phase1;

uint32_t phase2;

uint32_t phase3;

uint32_t phase4;

uint32_t phase5;

uint32_t phase6;

int32_t sum;

int8_t stage1;

int8_t stage2;

int ntrig1;

int32_t val1;

int ntrig2;

int32_t val2;

int64_t ccomp;

int64_t decay;

int64_t ENV1;int32_t offset;

MTOF(param_ofs, offset)

int32_t root;

MTOF(param_root, root)

int32_t spread;

MTOF(param_spread, spread)

int32_t t;

MTOF((1 << 27) - param_hit, t);

int32_t msine2;

int32_t msine3;

int32_t msine4;

int32_t msine5;

int32_t msine6;

SINE2TINTERP(param_rotate << 3, msine2)

SINE2TINTERP((param_rotate * 17) << 2, msine3)

SINE2TINTERP((param_rotate * 23) << 2, msine4)

SINE2TINTERP((param_rotate * 29) << 2, msine5)

SINE2TINTERP((param_rotate * 31) << 2, msine6)

MTOF(msine2 >> 5, msine2)

MTOF(msine3 >> 5, msine3)

MTOF(msine4 >> 5, msine4)

MTOF(msine5 >> 5, msine5)

MTOF(msine6 >> 5, msine6)// envelope

ccomp = (1 << 31) - val1;

decay = param_d2 - param_d1;

decay = ___SMMUL(val1 >> 1, decay << 2);

if ((inlet_gate > 0) && !ntrig1) {

ntrig1 = 1;

stage1 = 1;

} else if (!(inlet_gate > 0)) {

ntrig1 = 0;

}

if (stage1 == 0) {

val1 = ___SMMUL(val1, param_d1 + decay + (1 << 18) + (1 << 16)) << 1;

} else {

val1 = val1 + (t >> 7);

if (val1 < 0) {

val1 = 0x7FFFFFFF;

stage1 = 0;

}

}

ENV1 = val1 >> 4;

// phase oscillators

phase1 += root + offset;

phase2 += root - offset + spread * 7 + msine2;

phase3 += root + offset - spread * 5 + msine3;

phase4 += root + offset + spread * 3 + msine4;

phase5 += root - offset - spread * 2 + msine5;

phase6 += root - offset + spread + msine6;

// sine interpret

int32_t sine1;

int32_t sine2;

int32_t sine3;

int32_t sine4;

int32_t sine5;

int32_t sine6;

SINE2TINTERP(phase1, sine1)

SINE2TINTERP(phase2, sine2)

SINE2TINTERP(phase3, sine3)

SINE2TINTERP(phase4, sine4)

SINE2TINTERP(phase5, sine5)

SINE2TINTERP(phase6, sine6)

sum = (sine1 >> 8) + (sine2 >> 8) + (sine3 >> 8) + (sine4 >> 8) + (sine5 >> 8) +

(sine6 >> 8);

outlet_out = ___SMMUL(sum << 3, ENV1 << 3);