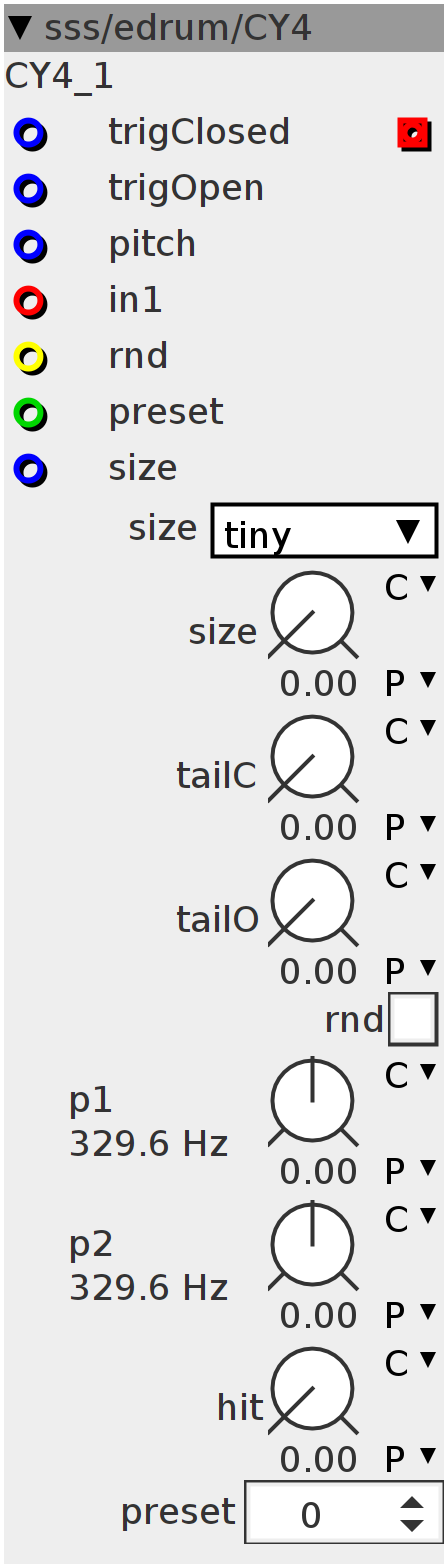

CY4

Cymbal/hihat generator based on fdn4 network. Seperate triggers for open&closed. 8 possible presets

Inlets

frac32buffer in1

bool32 rnd

int32 preset

frac32 trigClosed

frac32 trigOpen

frac32 pitch

frac32 size

Outlets

frac32buffer out1

Parameters

frac32.u.map size

frac32.u.map tailC

frac32.u.map tailO

frac32.u.map hit

bool32.tgl rnd

frac32.s.map.pitch p1

frac32.s.map.pitch p2

int32 preset

Attributes

combo size

static const uint32_t LENGTH = attr_size;

int32_t *d1d;

int32_t *d2d;

int32_t *d3d;

int32_t *d4d;

int32_t LM = attr_size - 1;

int32_t D[4];

int32_t S[32];

int i;

uint32_t d1p;

uint32_t d2p;

uint32_t d3p;

uint32_t d4p;

bool rtrg;

int32_t o1;

int32_t o2;

int32_t o3;

int32_t o4;

int32_t vl;

int32_t cnt;

bool gtrg;

int32_t env;

int32_t val[9];

int32_t NOISE(int32_t frq, int32_t I) {

I = I << 2;

val[I] = ___SMMLA((((int32_t)GenerateRandomNumber() >> 4) - val[I]) << 1, frq,

val[I]);

val[I + 1] = ___SMMLA((val[I] - val[I + 1]) << 1, frq, val[I + 1]);

val[I + 2] =

___SMMLA((val[I] - val[I + 1] - val[I + 2]) << 1, frq, val[I + 2]);

val[I + 3] = ___SMMLA((val[I + 2] - val[I + 3]) << 1, frq, val[I + 3]);

int32_t out;

return out = val[I + 2] - val[I + 3];

}

int32_t Dec;

int32_t f1;

int32_t f2;static int32_t _array1[LENGTH] __attribute__((section(".sdram")));

static int32_t _array2[LENGTH] __attribute__((section(".sdram")));

static int32_t _array3[LENGTH] __attribute__((section(".sdram")));

static int32_t _array4[LENGTH] __attribute__((section(".sdram")));

d1d = &_array1[0];

d2d = &_array2[0];

d3d = &_array3[0];

d4d = &_array4[0];

for (i = 0; i < attr_size; i++) {

d1d[i] = 0;

d2d[i] = 0;

d3d[i] = 0;

d4d[i] = 0;

}

d1p = 0;

d2p = 0;

d3p = 0;

d4p = 0;

for (i = 0; i < 32; i++) {

int32_t vol = (int32_t)GenerateRandomNumber() >> 4;

vol = ___SMMUL(vol << 3, (vol > 0 ? vol : -vol) << 2);

vol = (vol >> 1) + (1 << 26);

S[i] = vol;

}int preset = ((inlet_preset + param_preset) & 7) << 2;

bool GT = inlet_trigClosed || inlet_trigOpen;

cnt = __USAT(cnt - 1, 27);

if ((GT > 0) && !gtrg) {

MTOF(param_p1 + inlet_pitch, f1);

MTOF(param_p2 + inlet_pitch, f2);

if (inlet_trigOpen > 0) {

env = inlet_trigOpen;

Dec = param_tailO * 3 >> 2;

}

if (inlet_trigClosed > 0) {

env = inlet_trigClosed;

Dec = param_tailC * 3 >> 2;

}

cnt = (param_hit >> 20) + 4;

gtrg = 1;

} else if (GT <= 0) {

gtrg = 0;

}

int32_t DEC;

MTOF(-Dec, DEC)

DEC = DEC >> 3;

int32_t n1 = 0;

int32_t n2 = 0;

bool rnd = inlet_rnd && param_rnd;

if ((rnd > 0) && !rtrg) {

rtrg = 1;

for (i = 0; i < 4; i++) {

int32_t vol = (int32_t)GenerateRandomNumber() >> 4;

vol = ___SMMUL(vol << 3, (vol > 0 ? vol : -vol) << 2);

vol = (vol >> 1) + (1 << 26);

S[i + preset] = vol;

}

} else if (rnd == 0) {

rtrg = 0;

}

int32_t dec = (1 << 27) - Dec;

dec = ___SMMUL(dec << 3, dec << 2);

dec = (1 << 27) - ___SMMUL(dec << 3, dec << 2);

int32_t g2 = 755299123 + dec;

uint32_t size =

___SMMUL(attr_size - 1 << 3, __USAT(param_size + inlet_size, 27) << 2) + 1;

D[0] = ___SMMUL(size - 1 << 3, S[0 + preset] << 2) + 1;

D[1] = ___SMMUL(size - 1 << 2, S[1 + preset] << 2) + 1;

D[2] = ___SMMUL(size - 1 << 1, S[2 + preset] << 2) + 1;

D[3] = ___SMMUL(size - 1, S[3 + preset] << 2) + 1;env = ___SMMLA(-env << 1, DEC, env);

if (cnt > 0) {

n1 = NOISE(f1, 0);

n1 = NOISE(f2, 1);

}

int32_t i1 =

__SSAT(inlet_in1 + n1 + n2, 27) + __SSAT(d1d[(d1p + (o2 >> 24)) & LM], 27);

int32_t i2 = d2d[d2p];

int32_t i3 = d3d[d3p];

int32_t i4 = d4d[d4p];

int32_t t1 = i2 + i3;

int32_t t2 = -i1 - i4;

int32_t t3 = i1 - i4;

int32_t t4 = i2 - i3;

o1 = ___SMMLA(t1, g2, t1 >> 1);

o2 = ___SMMLA(t2, g2, t2 >> 1);

o3 = ___SMMLA(t3, g2, t3 >> 1);

o4 = ___SMMLA(t4, g2, t4 >> 1);

d1d[d1p] = __SSAT(o1, 28);

d2d[d2p] = __SSAT(o2, 28);

d3d[d3p] = __SSAT(o3, 28);

d4d[d4p] = __SSAT(o4, 28);

d1p++;

d2p++;

d3p++;

d4p++;

if (d1p >= D[0])

d1p = 0;

if (d2p >= D[1])

d2p = 0;

if (d3p >= D[2])

d3p = 0;

if (d4p >= D[3])

d4p = 0;

vl += o4 - vl >> 5;

int32_t out1 = o4 - vl << 2;

int32_t inv = (1 << 27) - env;

inv = (1 << 27) - ___SMMUL(inv << 3, inv << 2);

out1 = out1 > inv ? inv : out1;

out1 = out1 < -inv ? -inv : out1;

outlet_out = out1;