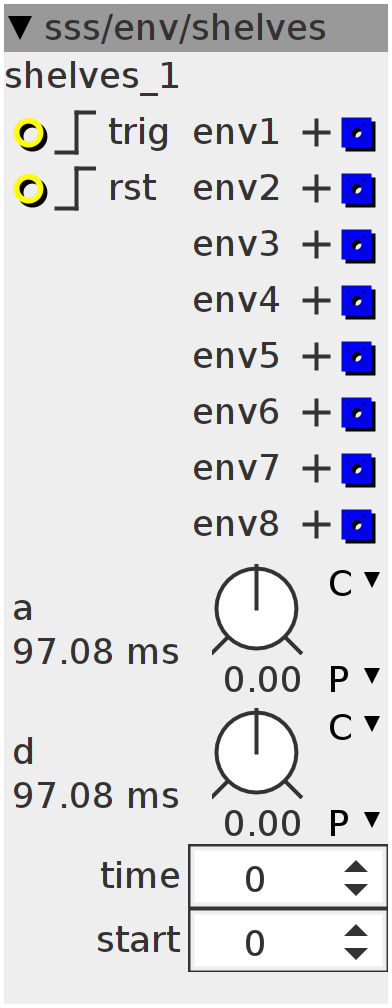

shelves

8x Attack/decay envelope, linear attack and decay envelope 1 is triggered at each high-gate at the trigger input. The other envelopes are triggered at a clock-divided rate. The clock-divisions to be used are set with the "time" knob. The clock-division also divides the slope-rates based on the A and D parameters. "start" offsets the reset-position. When zero, all clocks will trigger at first trigger after reset. Higher numbers will create different combinations of phase-relations between envelopes.

Inlets

bool32.rising trigger

bool32.rising rst

Outlets

frac32.positive envelope output

frac32.positive env2

frac32.positive env3

frac32.positive env4

frac32.positive env5

frac32.positive env6

frac32.positive env7

frac32.positive env8

Parameters

frac32.s.map.klineartime.exp a

frac32.s.map.klineartime.exp d

int32 time

int32 start

int8_t stage[8];

int ntrig;

int32_t val[8];

uint32_t cnt[8];

int i;

int tim[8][8] = {

{1, 2, 3, 4, 5, 6, 7, 8}, {1, 2, 4, 8, 16, 32, 64, 128},

{1, 2, 3, 4, 6, 8, 12, 16}, {1, 2, 3, 4, 8, 9, 16, 27},

{1, 3, 6, 9, 12, 15, 18, 21}, {1, 3, 9, 27, 81, 243, 729, 2187},

{1, 2, 4, 5, 8, 10, 15, 16}, {1, 2, 3, 4, 5, 6, 8, 10}};

bool rst;ntrig = 0;

for (i = 0; i < 8; i++) {

val[i] = 0;

}if ((inlet_rst > 0) && !rst) {

rst = 1;

for (i = 0; i < 8; i++) {

cnt[i] = tim[param_time][param_start];

}

} else if (inlet_rst == 0) {

rst = 0;

}

if ((inlet_trig > 0) && !ntrig) {

for (i = 0; i < 8; i++) {

if ((cnt[i] == 0) && (val[i] == 0)) {

stage[i] = 1;

}

cnt[i] += 1;

cnt[i] = cnt[i] >= tim[param_time][i] ? 0 : cnt[i];

}

ntrig = 1;

} else if (!(inlet_trig > 0)) {

ntrig = 0;

}

for (i = 0; i < 8; i++) {

if (stage[i] == 0) {

int32_t t;

MTOF(-param_d, t);

t = t / (tim[param_time][i]);

val[i] = __USAT(val[i] - (t >> 3), 31);

} else {

int32_t t;

MTOF(-param_a, t);

t = t / (tim[param_time][i]);

val[i] = val[i] + (t >> 3);

if (val[i] < 0) {

val[i] = 0x7FFFFFFF;

stage[i] = 0;

}

}

}

outlet_env1 = val[0] >> 4;

outlet_env2 = val[1] >> 4;

outlet_env3 = val[2] >> 4;

outlet_env4 = val[3] >> 4;

outlet_env5 = val[4] >> 4;

outlet_env6 = val[5] >> 4;

outlet_env7 = val[6] >> 4;

outlet_env8 = val[7] >> 4;