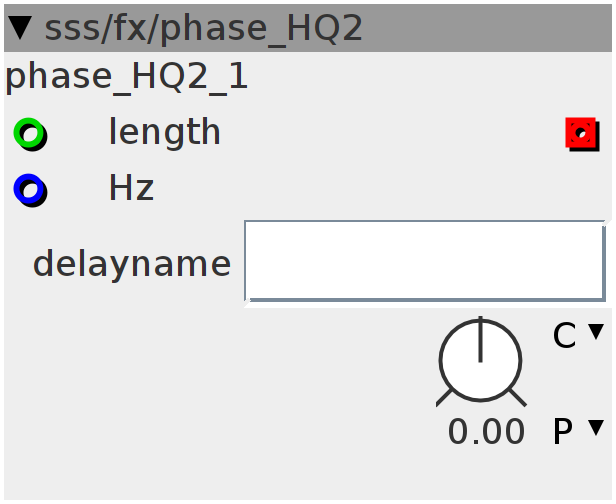

phase_HQ2

HQ phaser effect. Rate parameter is disconnected when the Hz-input is used! Use Hz input together with my Clock2Timing module (sss->timers) to sync the effect to host tempo. Set the recording delay to a high value (21.8s) to be able to morph from small to large modulation width. Then use an int-control to set the length of the phaser's counter (see delay's XML for the maximum "power" length sizes of the delay buffer). This modulation width can be controlled "realtime" and only sets till how far the counter can count. If count is higher then max, count will invert and slowely count back again.

Inlets

frac32 Connect to the Clock2Timing module (sss->Clock2Timing)

int32 Use int-control to set "power length" (see delay module for corresponding "power values"

Outlets

frac32buffer wave

Parameters

frac32.s.map rate

Attributes

objref delayname

Declaration

uint32_t phase1;

int64_t val;

int64_t ctrl0;

int64_t ctrl1;

int64_t ctrl2;

int64_t ctrl3;

int64_t ctrl4;

int64_t ctrl5;

int64_t ctrl6;

int64_t next1;

int64_t next2;

int64_t next3;

int64_t next4;

int64_t next5;

int64_t next6;

int64_t prev;

int64_t ccomp1;

int trg1;

int trg2;

int64_t dir;

int64_t val2;

int64_t out1;

int64_t out2;

int64_t sine1;

int64_t sine2;

Control Rate

// outlet_res=ctrl1<<28-inlet_length;

Audio Rate

int64_t freq = param_rate >> 4;

if (inlet_Hz) {

freq = ((inlet_Hz) / 44 * 30);

}

if (phase1 > (1 << 27)) {

trg1 = 1;

phase1 = (phase1 + (freq >> 2)) & ((1 << 27) - 1);

} else {

trg1 = 0;

phase1 += freq;

}

if (trg1 == 1) {

ctrl3 = ctrl2;

ctrl2 = ctrl1;

ctrl1 = ctrl0;

ctrl6 = ctrl5;

ctrl5 = ctrl4;

ctrl4 = (ctrl1 + (1 << inlet_length - 2)) & ((1 << inlet_length - 1) - 1);

if (ctrl1 >= ((1 << inlet_length - 1)))

ctrl0 = 0;

ctrl0 += 1;

}

ccomp1 = (1 << 27) - phase1;

SINE2TINTERP(((ctrl2 << (33 - inlet_length)) -

(phase1 >> (33 - inlet_length))) -

(1 << 30),

sine1)

sine1 = (sine1 >> 5) + (1 << 26);

sine2 = (1 << 27) - sine1;

uint32_t delay1 = attr_delayname.writepos - ctrl3 - BUFSIZE + buffer_index;

next1 = attr_delayname.array[delay1 & attr_delayname.LENGTHMASK] << 14;

uint32_t delay2 = attr_delayname.writepos - ctrl2 - BUFSIZE + buffer_index;

next2 = attr_delayname.array[delay2 & attr_delayname.LENGTHMASK] << 14;

uint32_t delay3 = attr_delayname.writepos - ctrl1 - BUFSIZE + buffer_index;

next3 = attr_delayname.array[delay3 & attr_delayname.LENGTHMASK] << 14;

uint32_t delay4 = attr_delayname.writepos - ctrl6 - BUFSIZE + buffer_index;

next4 = attr_delayname.array[delay4 & attr_delayname.LENGTHMASK] << 14;

uint32_t delay5 = attr_delayname.writepos - ctrl5 - BUFSIZE + buffer_index;

next5 = attr_delayname.array[delay5 & attr_delayname.LENGTHMASK] << 14;

uint32_t delay6 = attr_delayname.writepos - ctrl4 - BUFSIZE + buffer_index;

next6 = attr_delayname.array[delay6 & attr_delayname.LENGTHMASK] << 14;

out1 = (___SMMUL(ccomp1 << 3, next1 << 2) + next2 +

___SMMUL(phase1 << 3, next3 << 2)) >>

1;

out2 = (___SMMUL(ccomp1 << 3, next4 << 2) + next5 +

___SMMUL(phase1 << 3, next6 << 2)) >>

1;

out1 = ___SMMUL(out1 << 3, sine1 << 2);

out2 = ___SMMUL(out2 << 3, sine2 << 2);

val2 = val2 + (((out1 + out2) << 32) - val2) >> 1;

outlet_out = ((val2) >> 32) << 1;

// outlet_out=next1;

//(__USAT(param_time + inlet_time,27)>>(27-attr_delayname.LENGTHPOW))