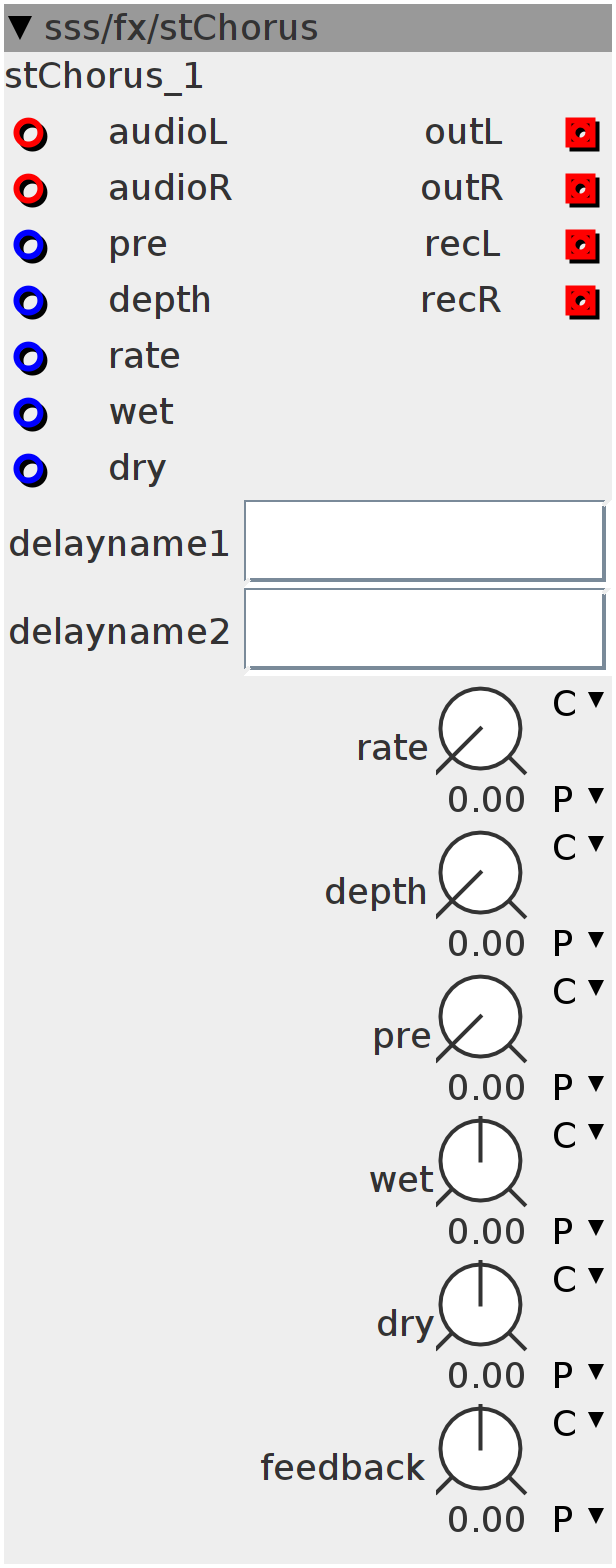

stChorus

stereo chorus module connect delay_write modules to the recL and recR output. Normal chorus setting would be 100ms max

Inlets

frac32 pre

frac32 depth

frac32 rate

frac32 wet

frac32 dry

frac32buffer audioL

frac32buffer audioR

Outlets

frac32buffer wave

frac32buffer outR

frac32buffer recL

frac32buffer recR

Parameters

frac32.u.map rate

frac32.u.map depth

frac32.u.map pre

frac32.s.map wet

frac32.s.map dry

frac32.s.map feedback

Attributes

objref delayname1

objref delayname2

uint32_t phase;

int32_t pre;

int32_t depth;

int32_t idepth;

int32_t Pre;

int32_t Depth;

int32_t Rate;pre = inlet_pre + param_pre;

depth = __USAT(inlet_depth + param_depth, 27);

depth = ___SMMUL(depth << 3, depth << 2);

idepth = (1 << 27) - depth;

int32_t pra = ___SMMUL(pre << 3, idepth << 2) + (depth >> 1);

int32_t rate = param_rate + inlet_rate;

rate = ___SMMUL(rate << 3, rate << 2) >> 6;

int32_t wet = param_wet + inlet_wet;

int32_t dry = param_dry + inlet_dry;Rate = Rate + ((rate - Rate) >> 6);

phase += Rate;

Pre = Pre + ((pra - Pre) >> 6);

Depth = Depth + ((depth - Depth) >> 6);

int32_t sine;

SINE2TINTERP(phase, sine)

int32_t read1 = __USAT(___SMMUL(Depth, sine >> 1) + Pre, 27);

int32_t read2 = __USAT(-___SMMUL(Depth, sine >> 1) + Pre, 27);

uint32_t tmp_d = read1;

uint32_t tmp_di = attr_delayname1.writepos -

(tmp_d >> (27 - attr_delayname1.LENGTHPOW)) - BUFSIZE +

buffer_index - 1;

uint32_t tmp_w1 = (tmp_d << (attr_delayname1.LENGTHPOW + 3)) & 0x3FFFFFFF;

uint32_t tmp_w2 = (1 << 30) - tmp_w1;

int32_t tmp_a1 = attr_delayname1.array[tmp_di & attr_delayname1.LENGTHMASK]

<< 16;

int32_t tmp_a2 =

attr_delayname1.array[(tmp_di + 1) & attr_delayname1.LENGTHMASK] << 16;

int32_t tmp_r = ___SMMUL(tmp_a1, tmp_w1);

tmp_r = ___SMMLA(tmp_a2, tmp_w2, tmp_r);

outlet_outL =

___SMMUL(dry << 3, inlet_audioL << 2) + ___SMMUL(wet << 3, tmp_r << 2);

outlet_recL = inlet_audioL + ___SMMUL(param_feedback << 3, tmp_r << 2);

tmp_d = read2;

tmp_di = attr_delayname2.writepos -

(tmp_d >> (27 - attr_delayname2.LENGTHPOW)) - BUFSIZE + buffer_index -

1;

tmp_w1 = (tmp_d << (attr_delayname2.LENGTHPOW + 3)) & 0x3FFFFFFF;

tmp_w2 = (1 << 30) - tmp_w1;

tmp_a1 = attr_delayname2.array[tmp_di & attr_delayname2.LENGTHMASK] << 16;

tmp_a2 = attr_delayname2.array[(tmp_di + 1) & attr_delayname2.LENGTHMASK] << 16;

tmp_r = ___SMMUL(tmp_a1, tmp_w1);

tmp_r = ___SMMLA(tmp_a2, tmp_w2, tmp_r);

outlet_outR =

___SMMUL(dry << 3, inlet_audioR << 2) + ___SMMUL(wet << 3, tmp_r << 2);

outlet_recR = inlet_audioR + ___SMMUL(param_feedback << 3, tmp_r << 2);