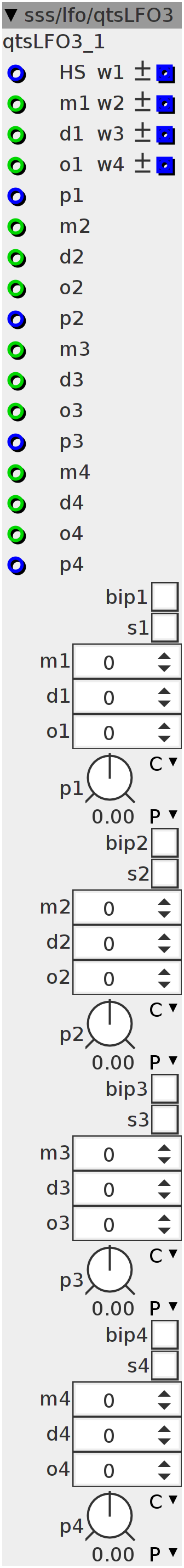

qtsLFO3

quad tempo synced sine wave LFO with inputs for multiplying, dividing and octaving the tempo and a phase-offset control.

Inlets

frac32 feed a LFO trigger/continuous signal to clock-sync the LFO.

frac32 phase offset

frac32 p2

frac32 p3

frac32 p4

int32 mutliply tempo

int32 divide tempo

int32 tempo octave down/up

int32 m2

int32 d2

int32 o2

int32 m3

int32 d3

int32 o3

int32 m4

int32 d4

int32 o4

Outlets

frac32.bipolar sine wave

frac32.bipolar w2

frac32.bipolar w3

frac32.bipolar w4

Parameters

bool32.tgl bip1

bool32.tgl s1

bool32.tgl bip2

bool32.tgl s2

bool32.tgl bip3

bool32.tgl s3

bool32.tgl bip4

bool32.tgl s4

int32 m1

int32 d1

int32 o1

int32 m2

int32 d2

int32 o2

int32 m3

int32 d3

int32 o3

int32 m4

int32 d4

int32 o4

frac32.s.map p1

frac32.s.map p2

frac32.s.map p3

frac32.s.map p4

uint32_t Phase[4];

int32_t sine[4];

int32_t M[4];

int32_t D[4];

float32_t O[4];

int32_t p[4];

int S[4];

int ttrig;

int32_t count;

int32_t timer;

float32_t rate;

int i;

int32_t tri(uint32_t P1, int instance) {

int32_t temp = P1 + (1 << 30);

temp = temp > 0 ? temp : -temp;

sine[instance] = (temp - (1 << 30)) << 1;

}rate = ((float32_t)(timer)) / ((float32_t)(48000));

rate = (((1 << 31) / 1500) / rate);

M[0] = param_m1 + inlet_m1;

M[1] = param_m2 + inlet_m2;

M[2] = param_m3 + inlet_m3;

M[3] = param_m4 + inlet_m4;

D[0] = param_d1 + inlet_d1;

D[1] = param_d2 + inlet_d2;

D[2] = param_d3 + inlet_d3;

D[3] = param_d4 + inlet_d4;

O[0] = param_o1 + inlet_o1 > 0

? (1 << param_o1 + inlet_o1)

: ((float32_t)(1)) / ((float32_t)(1 << -(param_o1 + inlet_o1)));

O[1] = param_o2 + inlet_o2 > 0

? (1 << param_o2 + inlet_o2)

: ((float32_t)(1)) / ((float32_t)(1 << -(param_o2 + inlet_o2)));

O[2] = param_o3 + inlet_o3 > 0

? (1 << param_o3 + inlet_o3)

: ((float32_t)(1)) / ((float32_t)(1 << -(param_o3 + inlet_o3)));

O[3] = param_o4 + inlet_o4 > 0

? (1 << param_o4 + inlet_o4)

: ((float32_t)(1)) / ((float32_t)(1 << -(param_o4 + inlet_o4)));

p[0] = inlet_p1 + param_p1;

p[1] = inlet_p2 + param_p2;

p[2] = inlet_p3 + param_p3;

p[3] = inlet_p4 + param_p4;

S[0] = param_s1;

S[1] = param_s2;

S[2] = param_s3;

S[3] = param_s4;

for (i = 0; i < 4; i++) {

Phase[i] += (((int32_t)((rate * M[i] / D[i]) * O[i])));

if (S[i] > 0) {

SINE2TINTERP(Phase[i] + (p[i] << 4), sine[i])

} else {

tri(Phase[i] + (p[i] << 4), i);

}

}

if (param_bip1 > 0) {

outlet_w1 = (sine[0] >> 4);

} else {

outlet_w1 = (sine[0] >> 5) + (1 << 26);

}

if (param_bip2 > 0) {

outlet_w2 = (sine[1] >> 4);

} else {

outlet_w2 = (sine[1] >> 5) + (1 << 26);

}

if (param_bip3 > 0) {

outlet_w3 = (sine[2] >> 4);

} else {

outlet_w3 = (sine[2] >> 5) + (1 << 26);

}

if (param_bip4 > 0) {

outlet_w4 = (sine[3] >> 4);

} else {

outlet_w4 = (sine[3] >> 5) + (1 << 26);

}if ((inlet_HS > 0) && (!(ttrig))) {

ttrig = 1;

timer = count;

count = 0;

} else if (!(inlet_HS > 0)) {

ttrig = 0;

}

count += 1;