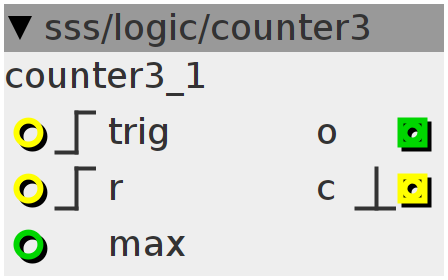

counter3

cyclic up counter added a trigger to the r output when the r-input gets triggered/is high (eg. active output of the clock module).

Inlets

int32 max

bool32.rising trigger

bool32.rising reset

Outlets

int32 output

bool32.pulse carry pulse

Declaration

int ntrig;

int rtrig;

int count;

Init

count = 0;

ntrig = 0;

rtrig = 0;

Control Rate

outlet_c = 0;

if ((inlet_trig > 0) && !ntrig) {

count += 1;

if (count >= inlet_max) {

count = 0;

outlet_c = 1;

}

ntrig = 1;

} else if (!(inlet_trig > 0))

ntrig = 0;

if ((inlet_r > 0) && !rtrig) {

count = 0;

rtrig = 1;

outlet_c = 1;

} else if (!(inlet_r > 0))

rtrig = 0;

outlet_o = count;