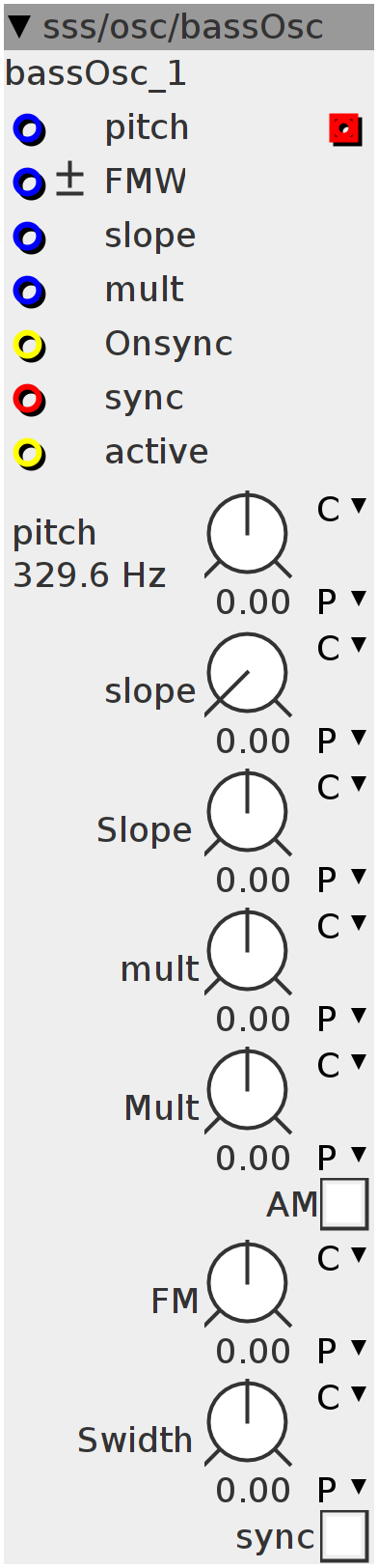

bassOsc

tri/saw oscillator with added sine ringmodulation for vowel-like or bass sounds

Inlets

frac32 pitch

frac32 slope

frac32 mult

frac32.bipolar FMW

bool32 Onsync

bool32 active

frac32buffer sync

Outlets

frac32buffer out

Parameters

frac32.s.map.pitch pitch

frac32.u.map slope

frac32.s.map Slope

frac32.s.map mult

frac32.s.map Mult

frac32.s.map FM

frac32.s.map Swidth

bool32.tgl AM

bool32.tgl sync

uint32_t Phase;

float32_t slope1n;

uint64_t slope1d;

uint64_t slope1e;

int32_t out;

int32_t sine;

int32_t Slope;

int32_t Fmw;

int32_t FMW;

int ttrig;

int32_t freq;

int32_t fmw;

int32_t sine1;

int32_t sine2;

int32_t mult;

int32_t Mult;if (inlet_active > 0) {

MTOF(param_pitch + inlet_pitch, freq)

fmw = __SSAT(param_FM + inlet_FMW, 29);

Mult = ___SMMUL((param_Mult) << 3, inlet_mult << 2) + param_mult;

}if (inlet_active > 0) {

if (((inlet_sync && (param_sync || inlet_Onsync)) > 0) && (!(ttrig == 1))) {

ttrig = 1;

Phase = 0;

} else if (inlet_sync < 0) {

ttrig = 0;

}

int32_t slape =

__SSAT(param_slope + ___SMMUL((inlet_slope) << 3, param_Slope << 2) +

___SMMUL(inlet_sync << 3, param_Swidth << 2),

28);

Slope = Slope + ((slape - Slope) >> 8);

Fmw = Fmw + ((fmw - Fmw) >> 6);

FMW = ___SMMUL(inlet_sync << 4, (Fmw) << 2);

Phase += freq + ___SMMUL(FMW << 4, freq << 4);

slope1d = (1 << 27) - Slope;

if (Phase < (Slope << 5)) {

slope1n = ((float)((1 << 31))) / ((float)(Slope));

out = ((Phase >> 5) * slope1n) + (1 << 30);

} else {

slope1n = ((float)((1 << 31))) / ((float)(slope1d));

out = -(((Phase - (Slope << 5)) >> 5) * slope1n) - (1 << 30);

}

mult = mult + ((Mult - mult) >> 8);

SINE2TINTERP((___SMMUL(out + (1 << 31), mult << 4) << 6) + (3 << 30), sine1)

SINE2TINTERP((___SMMUL(-out + (1 << 31), mult << 4) << 6) - (3 << 30), sine2)

outlet_out =

___SMMUL((((out >> 3)) + ___SMMUL(((out >> 4) + (1 << 27)), sine2) +

___SMMUL((1 << 28) - ((out >> 4) + (1 << 27)), sine1)),

((param_AM < 1 ? (1 << 28) : 0) +

___SMMUL(inlet_sync << 3, param_AM > 0 ? (1 << 30) : 0)))

<< 3;

}