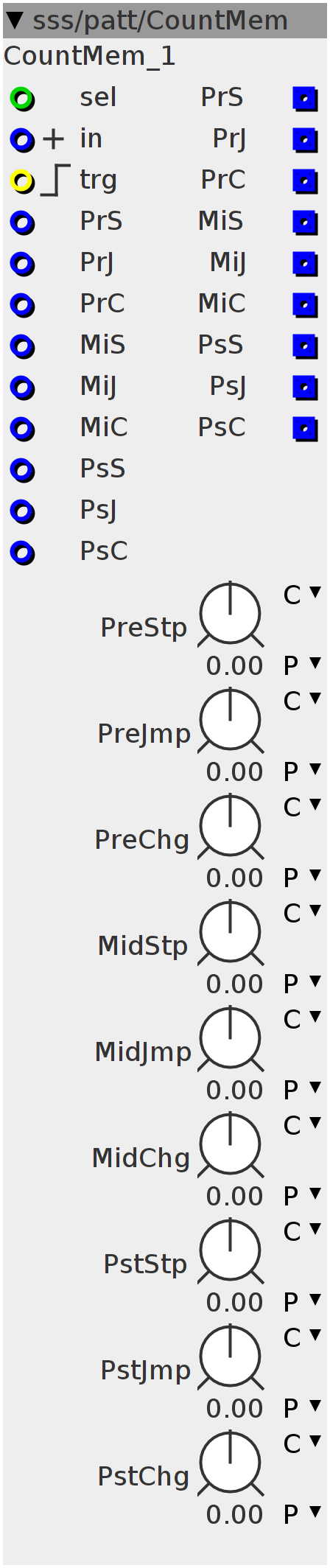

CountMem

parameter memory for the range counters

Inlets

frac32.positive input

bool32.rising trg

frac32 PrS

frac32 PrJ

frac32 PrC

frac32 MiS

frac32 MiJ

frac32 MiC

frac32 PsS

frac32 PsJ

frac32 PsC

int32 sel

Outlets

frac32 PrS

frac32 PrJ

frac32 PrC

frac32 MiS

frac32 MiJ

frac32 MiC

frac32 PsS

frac32 PsJ

frac32 PsC

Parameters

frac32.s.map PreStp

frac32.s.map PreJmp

frac32.s.map PreChg

frac32.s.map MidStp

frac32.s.map MidJmp

frac32.s.map MidChg

frac32.s.map PstStp

frac32.s.map PstJmp

frac32.s.map PstChg

int32_t cache;

int trg;switch (inlet_sel > 0 ? inlet_sel : 0) {

case 0:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PreStp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 1:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PreJmp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 2:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PreChg],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 3:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_MidStp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 4:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_MidJmp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 5:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_MidChg],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 6:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PstStp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 7:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PstJmp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 8:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PstChg],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

}

outlet_PrS = param_PreStp;

outlet_PrJ = param_PreJmp;

outlet_PrC = param_PreChg;

outlet_MiS = param_MidStp;

outlet_MiJ = param_MidJmp;

outlet_MiC = param_MidChg;

outlet_PsS = param_PstStp;

outlet_PsJ = param_PstJmp;

outlet_PsC = param_PstChg;