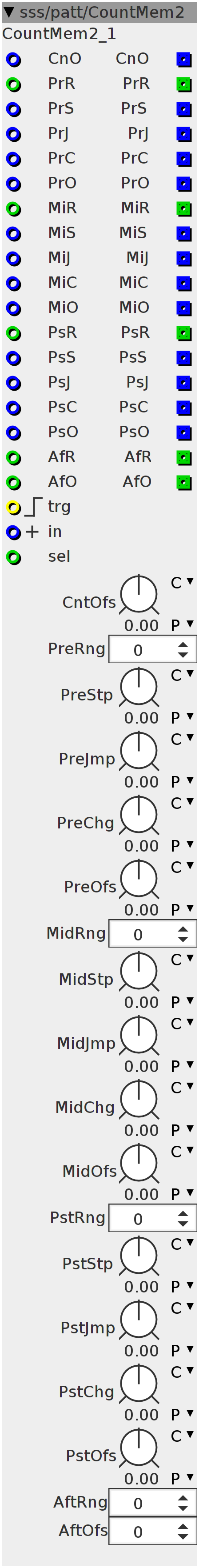

CountMem2

This is the control module for the quad counter/multiple single counter modules, based on the "range module" as I've called it for years, but here better known as the "divremc", a VERY usable module!

Inlets

int32 adds to respective value

int32 adds to respective value

int32 adds to respective value

int32 adds to respective value

int32 adds to respective value

int32 select parameter to change (0 to 17)

bool32.rising Trigger high updates parameter to "in" inlet

frac32.positive input for controlling parameters

frac32 adds to respective value, so no need for external adders.

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

frac32 adds to respective value

Outlets

frac32 CnO

frac32 PrS

frac32 PrJ

frac32 PrC

frac32 PrO

frac32 MiS

frac32 MiJ

frac32 MiC

frac32 MiO

frac32 PsS

frac32 PsJ

frac32 PsC

frac32 PsO

int32 Connect all parameters to corresponding inputs of the quad counter module or several single counter modules.

int32 MiR

int32 PsR

int32 AfR

int32 AfO

Parameters

int32 PreRng

int32 MidRng

int32 PstRng

int32 AftRng

int32 AftOfs

frac32.s.map CntOfs

frac32.s.map PreStp

frac32.s.map PreJmp

frac32.s.map PreChg

frac32.s.map PreOfs

frac32.s.map MidStp

frac32.s.map MidJmp

frac32.s.map MidChg

frac32.s.map MidOfs

frac32.s.map PstStp

frac32.s.map PstJmp

frac32.s.map PstChg

frac32.s.map PstOfs

int32_t cache;

int trg;switch (inlet_sel > 0 ? inlet_sel : 0) {

case 0:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_CntOfs],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 1:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PreRng],

inlet_in >> 17, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 2:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PreStp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 3:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PreJmp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 4:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PreChg],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 5:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PreOfs],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 6:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_MidRng],

inlet_in >> 17, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 7:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_MidStp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 8:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_MidJmp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 9:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_MidChg],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 10:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_MidOfs],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 11:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PstRng],

inlet_in >> 17, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 12:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PstStp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 13:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PstJmp],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 14:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PstChg],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 15:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_PstOfs],

inlet_in, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 16:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_AftRng],

inlet_in >> 17, 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

case 17:

if ((inlet_trg > 0) && (trg != 1)) {

trg = 1;

PExParameterChange(&parent->PExch[PARAM_INDEX_attr_legal_name_AftOfs],

(inlet_in >> 20) - (1 << 6), 0xFFFD);

} else {

if (inlet_trg == 0) {

trg = 0;

}

}

break;

}

outlet_CnO = param_CntOfs + inlet_CnO;

outlet_PrR = param_PreRng + inlet_PrR;

outlet_PrS = param_PreStp + inlet_PrS;

outlet_PrJ = param_PreJmp + inlet_PrJ;

outlet_PrC = param_PreChg + inlet_PrC;

outlet_PrO = param_PreOfs + inlet_PrO;

outlet_MiR = param_MidRng + inlet_MiR;

outlet_MiS = param_MidStp + inlet_MiS;

outlet_MiJ = param_MidJmp + inlet_MiJ;

outlet_MiC = param_MidChg + inlet_MiC;

outlet_MiO = param_MidOfs + inlet_MiO;

outlet_PsR = param_PstRng + inlet_PsR;

outlet_PsS = param_PstStp + inlet_PsS;

outlet_PsJ = param_PstJmp + inlet_PsJ;

outlet_PsC = param_PstChg + inlet_PsC;

outlet_PsO = param_PstOfs + inlet_PsO;

outlet_AfR = param_AftRng + inlet_AfR;

outlet_AfO = param_AftOfs + inlet_AfO;