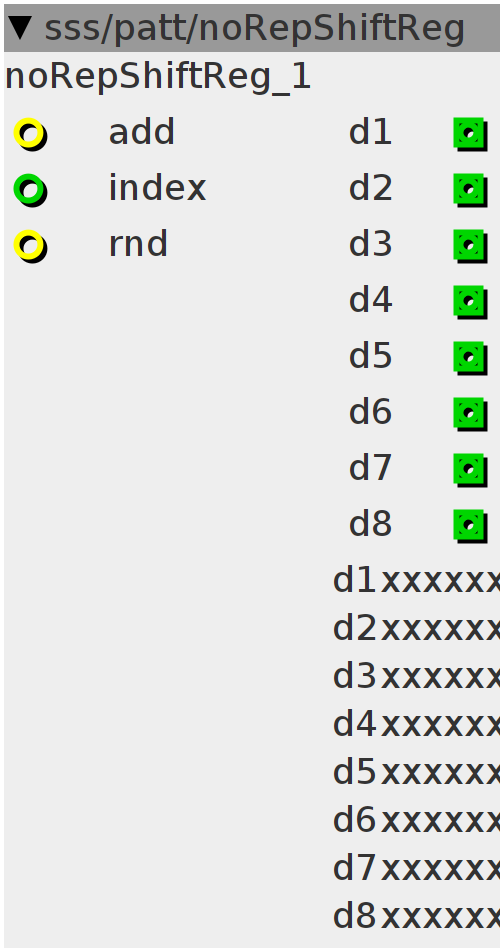

noRepShiftReg

No-repeating shift register When the add input goes high: -All values at the d1-d8 outputs will shift down one output, d8 will be removed. -Except when the new value is somewhere in the middle. In that case, this output is removed and only from the first output up to that output, the outputs are shifted down. -The value at the index input will always be send to the first output (d1) Useful for manually making orders of index numbers that may not be repeated in the order. eg. a set of footswitches that you can press to set an order of an fx-chain, where each footswitch selects it's own index number to enter. ps. if you only need 4 outputs, use the upper four.

Inlets

bool32 add

bool32 rnd

int32 index

Outlets

int32 d1

int32 d2

int32 d3

int32 d4

int32 d5

int32 d6

int32 d7

int32 d8

Displays

int32.label d1

int32.label d2

int32.label d3

int32.label d4

int32.label d5

int32.label d6

int32.label d7

int32.label d8

int A[8];

int w;

bool trg;

int i;

bool t;

int T;

bool rnd;

int B[8];

int left;for (i = 0; i < 8; i++) {

A[i] = i;

}if ((inlet_rnd > 0) && !rnd) {

rnd = 1;

for (i = 0; i < 8; i++) {

B[i] = i;

}

left = 8;

for (i = 0; i < 8; i++) {

int32_t tmp = (int32_t)(GenerateRandomNumber() % left);

left -= 1;

A[i] = B[tmp];

for (int j = tmp; j < (left); j++) {

B[j] = B[j + 1];

}

}

} else if (inlet_rnd < 1) {

rnd = 0;

}

if ((inlet_add > 0) && !trg) {

trg = 1;

T = -1;

for (i = 0; i < 8; i++) {

if (A[(w - i) & 7] == inlet_index) {

T = i;

}

}

if (T >= 0) {

for (i = T; i > 0; i--) {

A[(w - i) & 7] = A[(w - (i - 1)) & 7];

}

} else {

w = (w + 1) & 7;

}

A[w] = inlet_index;

} else if (inlet_add < 1) {

trg = 0;

}

outlet_d8 = disp_d8 = A[w];

outlet_d7 = disp_d7 = A[(w - 1) & 7];

outlet_d6 = disp_d6 = A[(w - 2) & 7];

outlet_d5 = disp_d5 = A[(w - 3) & 7];

outlet_d4 = disp_d4 = A[(w - 4) & 7];

outlet_d3 = disp_d3 = A[(w - 5) & 7];

outlet_d2 = disp_d2 = A[(w - 6) & 7];

outlet_d1 = disp_d1 = A[(w - 7) & 7];