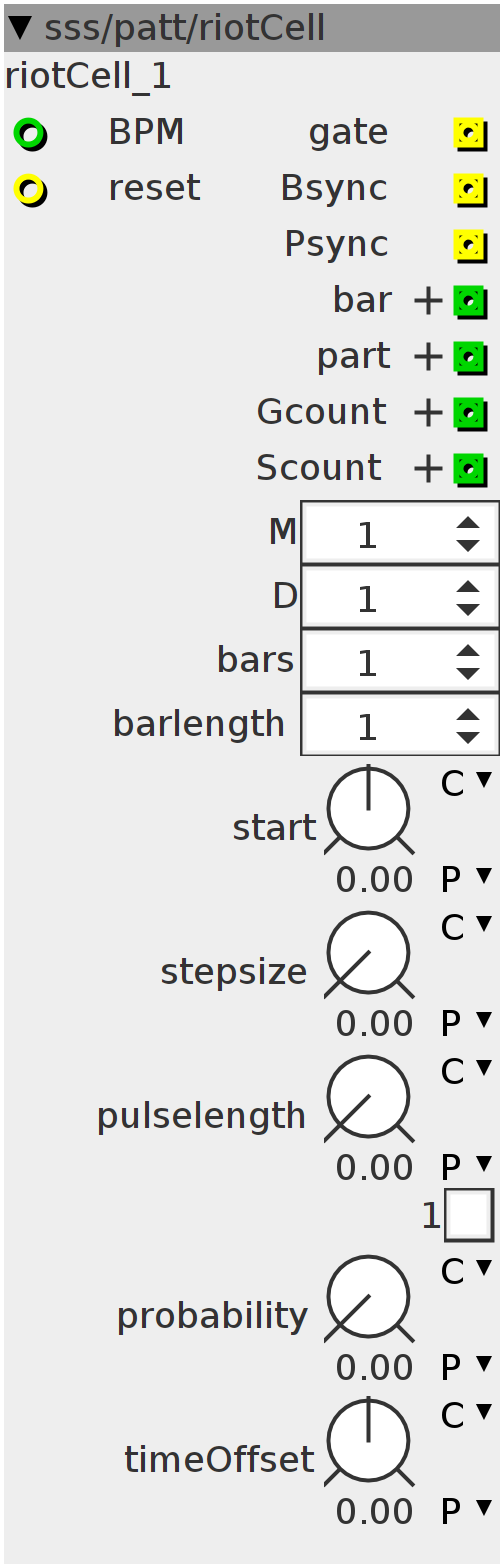

riotCell

This module is based on the trigger riot, though this can be seen as a single cell so you can set the size of your sequencer-matrix yourself. The module expects a main BPM value (just an integer control) All internal counters are reset at a trigger-high in the reset input. -M multiplies the main BPM, speeding up the clock in integer ratios -D divides the main clock, slowing the clock down in integer ratios -bars set how many times a bar is repeated -barlength sets the count-length of each bar the following settings are based upon the barlength: -start offsets the count within a bar, thereby offsetting the timing of the gate based on the set tempo and stepsize. -stepsize sets the euclidian stepsize, generating a beat every number of counts set by this control. So putting it to 16 will generate a gate at each quarter (->16/64) of the barlength. For a drum&bass kick with a barlength of 16, value would be around 41. The snare would have a start offset of 16 and stepsize of 32. -pulselength sets the length of the gate within the range of the stepsize. Set the "1" button to set minimum size to 1, otherwise low values will generate no gate (which would also be usable as a "mute" control). -probability sets the chance that at any given count a random gate is being generated. -timeoffset offsets the internal LFO which triggers the counter, thereby offsetting the count, but not fixed to the main tempo. It's more like a clock-swing.

Inlets

int32 BPM

bool32 reset

Outlets

int32.positive bar

int32.positive part

int32.positive Gcount

int32.positive Scount

bool32 gate

bool32 Bsync

bool32 Psync

Parameters

int32 M

int32 D

int32 bars

int32 barlength

frac32.s.map start

frac32.s.map timeOffset

frac32.u.map stepsize

frac32.u.map pulselength

frac32.u.map probability

bool32.tgl 1

uint32_t count;

uint32_t Count;

uint32_t part;

int ntrig;

int trig;

int length;

int C1;

int C2;

int C3;

int G;

int gate;

int32_t stepsize;

int32_t pulsewidth;

int nextbar;

int Brestart;

int rndgate;

int rtrig;if ((inlet_reset > 0) && !rtrig == 1) {

rtrig = 1;

count = 0;

C1 = 0;

C2 = 0;

} else if (inlet_reset == 0) {

rtrig = 0;

}

int32_t rate;

rate = (1 << 29) / (48000 >> 7) * inlet_BPM / 60 * param_M / param_D;

count += rate;

Count = count + (param_timeOffset << 5);

length = param_barlength;

stepsize = ___SMMUL(param_barlength << 3, param_stepsize << 2);

pulsewidth =

___SMMUL((stepsize - param_1) << 3, param_pulselength << 2) + param_1;

trig = Count < (1 << 31) ? 1 : 0;

nextbar = 0;

if ((trig > 0) && !ntrig) {

ntrig = 1;

C1 += 1;

nextbar = C1 >= length ? 1 : 0;

C1 = C1 >= length ? 0 : C1;

rndgate = ((int32_t)(GenerateRandomNumber()) >> 4) <

((param_probability << 1) - (1 << 27))

? 1

: 0;

} else if (trig == 0) {

ntrig = 0;

}

Brestart = 0;

if (nextbar > 0) {

C2 += 1;

Brestart = C2 >= param_bars ? 1 : 0;

C2 = C2 >= param_bars ? 0 : C2;

}

G = C1 - ___SMMUL(param_start << 3, length << 2);

G = G - (G / length) * length;

G = G < 0 ? G + length : G;

gate = G - (G / stepsize) * stepsize;

outlet_Gcount = gate;

outlet_Scount = G / stepsize;

gate = gate < 0 ? gate + stepsize : gate;

gate = gate < pulsewidth ? 1 : 0;

outlet_gate = gate + rndgate;

outlet_Bsync = Brestart;

outlet_Psync = nextbar;

outlet_bar = C2;

outlet_part = C1;