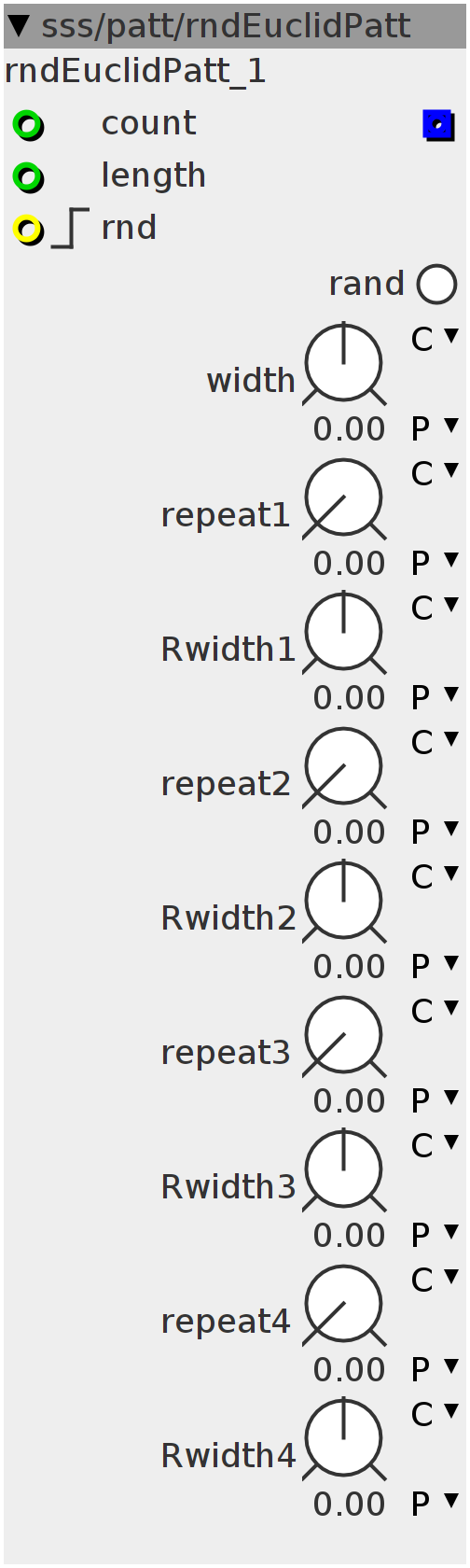

rndEuclidPatt

combined euclidian and random pattern generator connect "COUNT" to a counter (sss-logic) connect "LENGTH" to the max-count control width sets the level of the random sequence REPEAT(1-4) set an euclidian division over the entire length, generating gates. The smaller the value, the smaller the steps and the more gates will be generated. Rwidth(1-4) set the width of the euclidian gates, being added to the pattern.

Inlets

int32 count

int32 length

bool32.rising rnd

Outlets

frac32 rand

Parameters

bool32.mom rand

frac32.s.map width

frac32.s.map Rwidth1

frac32.s.map Rwidth2

frac32.s.map Rwidth3

frac32.s.map Rwidth4

frac32.u.map repeat1

frac32.u.map repeat2

frac32.u.map repeat3

frac32.u.map repeat4

int32_t _val[128];

int32_t vol;

int ntrig;

int8_t lng;

int i;for (i = 0; i < 128; i++)

_val[i] = (GenerateRandomNumber()) >> 4;

{}

ntrig = 0;int32_t repeat1 = ___SMMUL(param_repeat1 << 3, inlet_length << 2);

int32_t gtrig1 = inlet_count - ((inlet_count / repeat1) * repeat1);

gtrig1 = gtrig1 == 0 ? (1 << 27) : 0;

int32_t repeat2 = ___SMMUL(param_repeat2 << 3, inlet_length << 2);

int32_t gtrig2 = inlet_count - ((inlet_count / repeat2) * repeat2);

gtrig2 = gtrig2 == 0 ? (1 << 27) : 0;

int32_t repeat3 = ___SMMUL(param_repeat3 << 3, inlet_length << 2);

int32_t gtrig3 = inlet_count - ((inlet_count / repeat3) * repeat3);

gtrig3 = gtrig3 == 0 ? (1 << 27) : 0;

int32_t repeat4 = ___SMMUL(param_repeat4 << 3, inlet_length << 2);

int32_t gtrig4 = inlet_count - ((inlet_count / repeat4) * repeat4);

gtrig4 = gtrig4 == 0 ? (1 << 27) : 0;

lng = inlet_length;

if (((param_rand + inlet_rnd) > 0) && (!(ntrig))) {

for (i = 0; i < lng; i++)

_val[i] = (GenerateRandomNumber()) >> 4;

{}

ntrig = 1;

} else if (!((param_rand + inlet_rnd) > 0)) {

ntrig = 0;

}

vol = _val[inlet_count];

outlet_rand = ___SMMUL(vol << 2, param_width << 2) +

___SMMUL(gtrig1 << 3, param_Rwidth1 << 2) +

___SMMUL(gtrig2 << 3, param_Rwidth2 << 2) +

___SMMUL(gtrig3 << 3, param_Rwidth3 << 2) +

___SMMUL(gtrig4 << 3, param_Rwidth4 << 2);