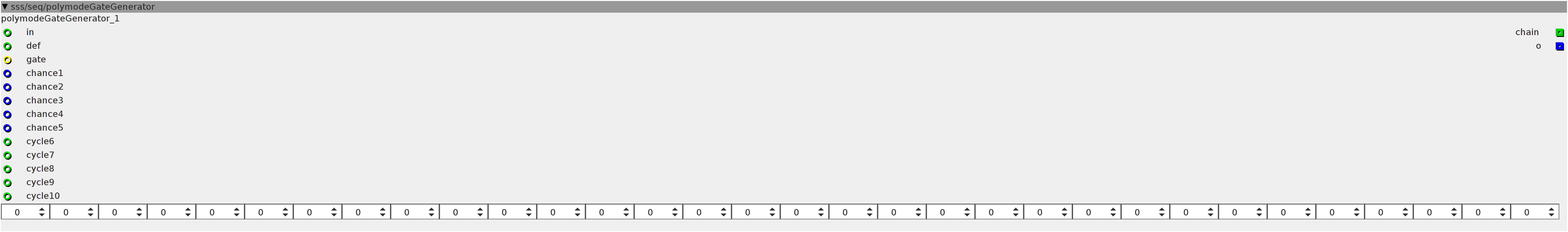

polymodeGateGenerator

A gate sequencer with 16 different "modes" for each step, allowing for a more or less recognizable but changing gate-sequence 0=gate OFF 1 to 5 are chance-controlled, set by the chance inputs. So when a step is set to 5 and the chance5 input is at 32, theres a 50% chance that it will generate a gate. 6-10 are "cycle" inputs. So, eg. when cycle6 is set to 3, an internal counter is triggered each time the sequencer comes along a step set to "6". Only when the internal counter is 0, a gate is generated. 11-12 are selected by an internal 0/1 counter that is triggered at each first step of the sequence. When it's 0, it will play the "11" steps, when 1, it will play the "12" steps. 13-16 are the same like above, but the internal counter will count 0, 1, 2, 3 (-> 13, 14 ,15, 16)

Inlets

int32 in

int32 default value

int32 cycle6

int32 cycle7

int32 cycle8

int32 cycle9

int32 cycle10

bool32 gate

frac32 chance1

frac32 chance2

frac32 chance3

frac32 chance4

frac32 chance5

Outlets

frac32 o

int32 chain out (in-32)

Parameters

int32.mini i0

int32.mini i1

int32.mini i2

int32.mini i3

int32.mini i4

int32.mini i5

int32.mini i6

int32.mini i7

int32.mini i8

int32.mini i9

int32.mini i10

int32.mini i11

int32.mini i12

int32.mini i13

int32.mini i14

int32.mini i15

int32.mini i16

int32.mini i17

int32.mini i18

int32.mini i19

int32.mini i20

int32.mini i21

int32.mini i22

int32.mini i23

int32.mini i24

int32.mini i25

int32.mini i26

int32.mini i27

int32.mini i28

int32.mini i29

int32.mini i30

int32.mini i31

int32_t val;

bool rnd;

int cnt[8];cnt[6] = -1;

cnt[7] = -1;int32_t o;

bool DO = 0;

if ((inlet_gate > 0) && !rnd) {

DO = 1;

cnt[6] += inlet_in == 0 ? 1 : 0;

cnt[6] = cnt[6] & 1;

cnt[7] += inlet_in == 0 ? 1 : 0;

cnt[7] = cnt[7] & 3;

rnd = 1;

val = (int32_t)(GenerateRandomNumber() >> 5);

} else if (inlet_gate == 0) {

rnd = 0;

}

switch (inlet_in) {

case 0:

o = param_i0;

break;

case 1:

o = param_i1;

break;

case 2:

o = param_i2;

break;

case 3:

o = param_i3;

break;

case 4:

o = param_i4;

break;

case 5:

o = param_i5;

break;

case 6:

o = param_i6;

break;

case 7:

o = param_i7;

break;

case 8:

o = param_i8;

break;

case 9:

o = param_i9;

break;

case 10:

o = param_i10;

break;

case 11:

o = param_i11;

break;

case 12:

o = param_i12;

break;

case 13:

o = param_i13;

break;

case 14:

o = param_i14;

break;

case 15:

o = param_i15;

break;

case 16:

o = param_i16;

break;

case 17:

o = param_i17;

break;

case 18:

o = param_i18;

break;

case 19:

o = param_i19;

break;

case 20:

o = param_i20;

break;

case 21:

o = param_i21;

break;

case 22:

o = param_i22;

break;

case 23:

o = param_i23;

break;

case 24:

o = param_i24;

break;

case 25:

o = param_i25;

break;

case 26:

o = param_i26;

break;

case 27:

o = param_i27;

break;

case 28:

o = param_i28;

break;

case 29:

o = param_i29;

break;

case 30:

o = param_i30;

break;

case 31:

o = param_i31;

break;

default:

o = inlet_def;

}

int32_t A = 0;

if (o > 0) {

int B = o - 5;

switch ((o - 1) & 15) {

case 0:

A = (inlet_gate && (val < inlet_chance1)) << 27;

break;

case 1:

A = (inlet_gate && (val < inlet_chance2)) << 26;

break;

case 2:

A = (inlet_gate && (val < inlet_chance3)) << 26;

break;

case 3:

A = (inlet_gate && (val < inlet_chance4)) << 26;

break;

case 4:

A = (inlet_gate && (val < inlet_chance4)) << 26;

break;

case 5:

if (DO > 0) {

cnt[B] += 1;

cnt[B] = cnt[B] > inlet_cycle6 ? 0 : cnt[B];

};

A = (inlet_gate && (cnt[B] == 0)) << 26;

break;

case 6:

if (DO > 0) {

cnt[B] += 1;

cnt[B] = cnt[B] > inlet_cycle7 ? 0 : cnt[B];

};

A = (inlet_gate && (cnt[B] == 0)) << 26;

break;

case 7:

if (DO > 0) {

cnt[B] += 1;

cnt[B] = cnt[B] > inlet_cycle8 ? 0 : cnt[B];

};

A = (inlet_gate && (cnt[B] == 0)) << 26;

break;

case 8:

if (DO > 0) {

cnt[B] += 1;

cnt[B] = cnt[B] > inlet_cycle9 ? 0 : cnt[B];

};

A = (inlet_gate && (cnt[B] == 0)) << 26;

break;

case 9:

if (DO > 0) {

cnt[B] += 1;

cnt[B] = cnt[B] > inlet_cycle10 ? 0 : cnt[B];

};

A = (inlet_gate && (cnt[B] == 0)) << 26;

break;

case 10:

A = (inlet_gate && (cnt[6] == 0)) << 27;

break;

case 11:

A = (inlet_gate && (cnt[6] == 1)) << 27;

break;

case 12:

A = (inlet_gate && (cnt[7] == 0)) << 27;

break;

case 13:

A = (inlet_gate && (cnt[7] == 1)) << 27;

break;

case 14:

A = (inlet_gate && (cnt[7] == 2)) << 27;

break;

case 15:

A = (inlet_gate && (cnt[7] == 3)) << 27;

break;

}

}

outlet_o = A;

outlet_chain = inlet_in - 32;