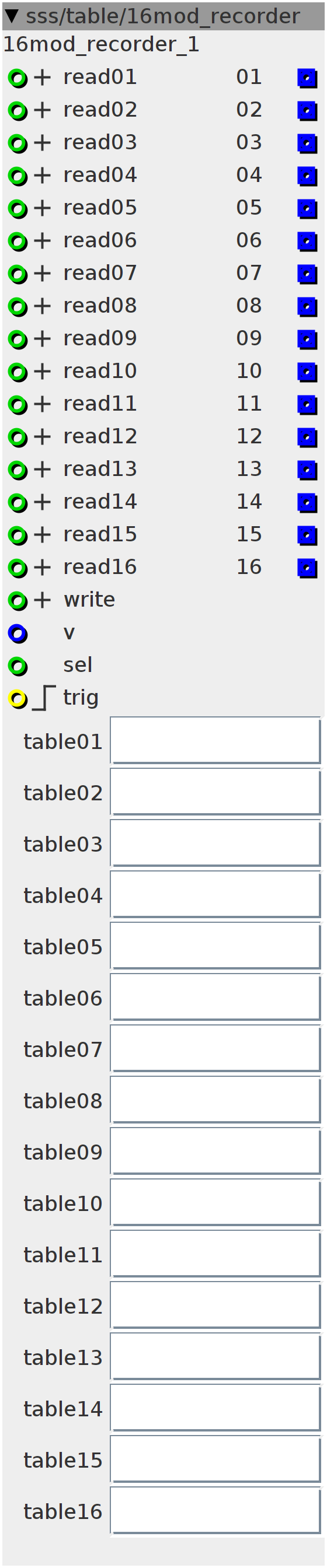

16mod_recorder

16 output modulation recorder

Inlets

int32 sel

bool32.rising trigger

int32.positive read01

int32.positive read02

int32.positive read03

int32.positive read04

int32.positive read05

int32.positive read06

int32.positive read07

int32.positive read08

int32.positive read09

int32.positive read10

int32.positive read11

int32.positive read12

int32.positive read13

int32.positive read14

int32.positive read15

int32.positive read16

int32.positive index (integer, not fraction)

frac32 value

Outlets

frac32 01

frac32 02

frac32 03

frac32 04

frac32 05

frac32 06

frac32 07

frac32 08

frac32 09

frac32 10

frac32 11

frac32 12

frac32 13

frac32 14

frac32 15

frac32 16

Attributes

objref table01

objref table02

objref table03

objref table04

objref table05

objref table06

objref table07

objref table08

objref table09

objref table10

objref table11

objref table12

objref table13

objref table14

objref table15

objref table16

int ntrig;int ntrig = 0;switch (inlet_sel > 0 ? inlet_sel : 0) {

case 0:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table01.LENGTH)

attr_table01.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table01.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 1:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table02.LENGTH)

attr_table02.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table02.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 2:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table03.LENGTH)

attr_table03.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table03.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 3:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table04.LENGTH)

attr_table04.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table04.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 4:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table05.LENGTH)

attr_table05.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table05.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 5:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table06.LENGTH)

attr_table06.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table06.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 6:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table07.LENGTH)

attr_table07.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table07.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 7:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table08.LENGTH)

attr_table08.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table08.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 8:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table09.LENGTH)

attr_table09.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table09.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 9:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table10.LENGTH)

attr_table10.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table10.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 10:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table11.LENGTH)

attr_table11.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table11.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 11:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table12.LENGTH)

attr_table12.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table12.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 12:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table13.LENGTH)

attr_table13.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table13.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 13:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table14.LENGTH)

attr_table14.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table14.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 14:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table15.LENGTH)

attr_table15.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table15.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

case 15:

if ((inlet_trig > 0) && !ntrig) {

ntrig = 1;

if (inlet_write < attr_table16.LENGTH)

attr_table16.array[inlet_write] =

__SSAT(inlet_v, 28) >> attr_table16.GAIN;

}

if (!(inlet_trig > 0))

ntrig = 0;

break;

default:

break;

}

outlet_01 = attr_table01.array[__USAT(inlet_read01, attr_table01.LENGTHPOW)]

<< attr_table01.GAIN;

outlet_02 = attr_table02.array[__USAT(inlet_read02, attr_table02.LENGTHPOW)]

<< attr_table02.GAIN;

outlet_03 = attr_table03.array[__USAT(inlet_read03, attr_table03.LENGTHPOW)]

<< attr_table03.GAIN;

outlet_04 = attr_table04.array[__USAT(inlet_read04, attr_table04.LENGTHPOW)]

<< attr_table04.GAIN;

outlet_05 = attr_table05.array[__USAT(inlet_read05, attr_table05.LENGTHPOW)]

<< attr_table05.GAIN;

outlet_06 = attr_table06.array[__USAT(inlet_read06, attr_table06.LENGTHPOW)]

<< attr_table06.GAIN;

outlet_07 = attr_table07.array[__USAT(inlet_read07, attr_table07.LENGTHPOW)]

<< attr_table07.GAIN;

outlet_08 = attr_table08.array[__USAT(inlet_read08, attr_table08.LENGTHPOW)]

<< attr_table08.GAIN;

outlet_09 = attr_table09.array[__USAT(inlet_read09, attr_table09.LENGTHPOW)]

<< attr_table09.GAIN;

outlet_10 = attr_table10.array[__USAT(inlet_read10, attr_table10.LENGTHPOW)]

<< attr_table10.GAIN;

outlet_11 = attr_table11.array[__USAT(inlet_read11, attr_table11.LENGTHPOW)]

<< attr_table11.GAIN;

outlet_12 = attr_table12.array[__USAT(inlet_read12, attr_table12.LENGTHPOW)]

<< attr_table12.GAIN;

outlet_13 = attr_table13.array[__USAT(inlet_read13, attr_table13.LENGTHPOW)]

<< attr_table13.GAIN;

outlet_14 = attr_table14.array[__USAT(inlet_read14, attr_table14.LENGTHPOW)]

<< attr_table14.GAIN;

outlet_15 = attr_table15.array[__USAT(inlet_read15, attr_table16.LENGTHPOW)]

<< attr_table15.GAIN;

outlet_16 = attr_table16.array[__USAT(inlet_read16, attr_table16.LENGTHPOW)]

<< attr_table16.GAIN;