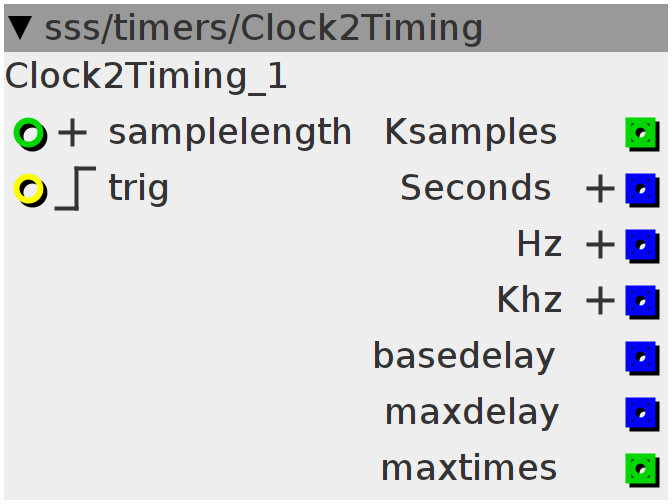

Clock2Timing

measures the time interval between triggers and converts them into several usable data

Inlets

int32.positive Set bits of max delay length (delay write module setting)

bool32.rising Timing calculation is based on incoming clock.

Outlets

frac32 basedelay

frac32 maxdelay

int32 time interval in k-rate ticks (0.333ms)

int32 maxtimes

frac32.positive Seconds

frac32.positive Hz

frac32.positive Khz

int ntrig;

int rtrig;

int count;

int32_t trigstart;

int32_t trigstop;

int32_t tc;

int32_t tlatch;

int32_t s;

int32_t t;count = 0;

ntrig = 0;

rtrig = 0;

trigstart = 0;

trigstop = 0;

tlatch = (1 << 31);

tc = (1 << 31);

t = 1;

s = tlatch;int c;

c = 0;

if ((inlet_trig > 0) && !ntrig) {

count += 1;

if (count >= 2) {

count = 0;

c = 1;

}

ntrig = 1;

} else if (!(inlet_trig > 0))

ntrig = 0;

outlet_Seconds = ((tlatch << 13) / 48000) << 8;

outlet_Hz = 4398046500000.f / outlet_Seconds;

outlet_Khz = outlet_Hz / 1000;

outlet_Ksamples = tlatch;

int r;

r = ((unsigned int)(1 << inlet_samplelength)) / tlatch;

outlet_maxtimes = r;

outlet_maxdelay = ((r * tlatch * 64) / (1 << inlet_samplelength)) << 21;

outlet_basedelay = ((tlatch * (1 << 14)) / (1 << inlet_samplelength)) << 13;

if ((s * 2) < (1 << inlet_samplelength)) {

t = t + 1;

}

s = tlatch * (1 << t);

if ((s) > (1 << inlet_samplelength)) {

t = t - 1;

}

s = tlatch * (1 << t);if ((c > 0) && !trigstart) {

tc = 0;

trigstart = 1;

} else if (!(c > 0)) {

trigstart = 0;

}

if ((count > 0) && !trigstop) {

tlatch = tc;

trigstop = 1;

} else if (!(count > 0)) {

trigstop = 0;

}

tc++;