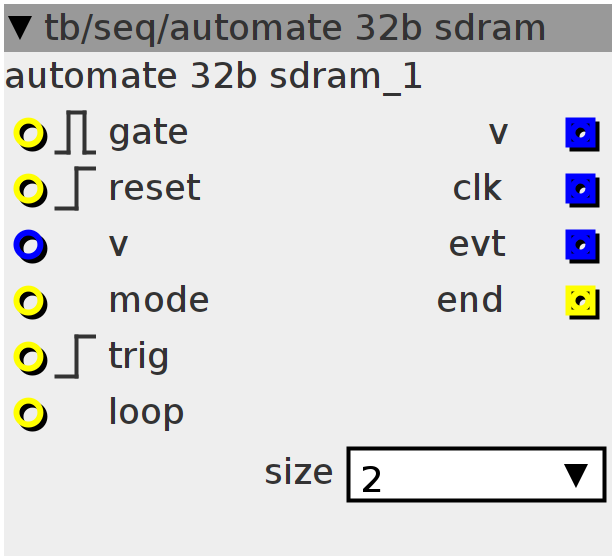

automate 32b sdram

automate events SDRAM memory

Inlets

frac32 value

bool32 play/record

bool32 loop

bool32.risingfalling gate

bool32.rising reset

bool32.rising clock

Outlets

frac32 value

frac32 clock

frac32 event

bool32 end

Attributes

combo size

static const uint32_t LENGTHPOW = attr_size;

static const uint32_t LENGTH = 1 << attr_size;

static const uint32_t LENGTHMASK = (1 << attr_size) - 1;

static const uint32_t BITS = 32;

int32_t *_time;

int32_t *_data;

int32_t _t;

int32_t _idx;

int32_t _endidx;

int32_t _endt;

int32_t _end;

int32_t _value;

bool _record;

int32_t _gate;

int32_t _reset;

int32_t _running;

int32_t _trig;{

static int32_t _timeArray[attr_poly][LENGTH]

__attribute__((section(".sdram")));

_time = &_timeArray[parent->polyIndex][0];

static int32_t _dataArray[attr_poly][LENGTH]

__attribute__((section(".sdram")));

_data = &_dataArray[parent->polyIndex][0];

int i;

for (i = 0; i < LENGTH; i++) {

_time[i] = 0;

_data[i] = 0;

}

_t = 0;

_idx = 0;

_endidx = 0;

_running = 0;

_value = 0;

_reset = 0;

_record = 0;

_trig = 0;

_endt = 0;

_end = 0;

}{

_end = 0;

if (inlet_reset > 0 & !_reset) {

_reset = inlet_reset;

_idx = 0;

_t = 0;

_running = _gate;

} else {

_reset = 0;

}

if (inlet_gate != _gate && inlet_gate > 0) {

_idx = 0;

_t = 0;

_running = 1;

}

if (inlet_mode != _record && inlet_mode > 0) {

// entering record

_record = 1;

_idx = 0;

_t = 0;

}

if (inlet_mode != _record && !inlet_mode) {

// entering play

_record = 0;

_endt = _t;

_endidx = _idx;

_idx = 0;

_t = 0;

}

if ((inlet_trig > 0) && !_trig) {

if (_running) {

_t++;

}

_trig = 1;

} else if (!(inlet_trig > 0))

_trig = 0;

if (_record) {

// record mode

if (inlet_gate != _gate && inlet_gate > 0) {

_endidx = LENGTH;

}

if (_running && inlet_v != _value) {

_value = inlet_v;

_time[_idx] = _t;

_data[_idx] = _value;

if (_idx < LENGTH) {

_idx++;

} else {

// at end of recording, start playing back

_end = 1;

_endidx = _idx;

_endt = _t;

_record = 0;

_idx = 0;

_t = 0;

_running = inlet_loop;

}

}

if (inlet_gate != _gate && !inlet_gate) {

_endidx = _idx;

_endt = _t;

}

} else {

// play mode

// if(inlet_gate != _gate && inlet_gate>0) { }

if (_running) {

if (_t >= _time[_idx]) {

_value = _data[_idx];

if (_idx < LENGTH && _idx < _endidx) {

_idx++;

}

}

if (_t >= _endt && _idx >= _endidx) {

_end = 1;

_t = 0;

_idx = 0;

_running = inlet_loop;

}

}

// if(inlet_gate != _gate && !inlet_gate) { }

}

if (inlet_gate != _gate && !inlet_gate) {

_running = 0;

}

_gate = inlet_gate;

outlet_end = _end;

outlet_evt = _idx;

outlet_clk = _t;

outlet_v = _value;

}