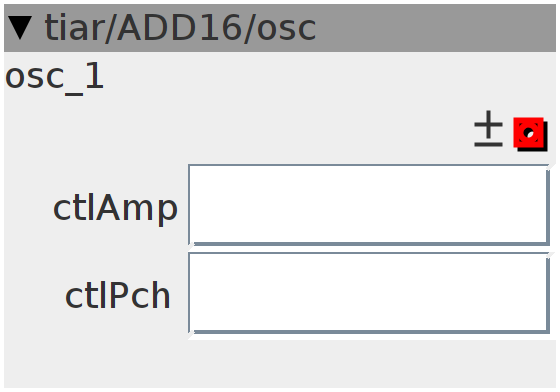

osc

ADD16 osc, needs to connect to a ADD16 controller. Experimental.

Inlets

None

Outlets

frac32buffer.bipolar out

Attributes

objref ctlAmp

objref ctlPch

Declaration

static const uint32_t NBH = 16;

uint32_t t_p[NBH];

int32_t t_g[NBH];

uint32_t getDp(int h) { return attr_ctlPch.getDp(h); }

// anti aliasing

uint32_t getGain(int h) {

if (getDp(h) > 0x007FFFFFU)

return 0;

else

return attr_ctlAmp.getGain(h);

}

Init

for (int h = 0; h < NBH; h++) {

t_p[h] = 0;

t_g[h] = 0;

}

Control Rate

uint32_t p = t_p[0];

int32_t g = t_g[0];

uint32_t dp = getDp(0);

for (int i = 0; i < BUFSIZE; i++) {

p += dp;

if (p > 0x00FFFFFF) {

p &= 0x00FFFFFF;

g = getGain(0);

}

outlet_out[i] = ___SMMUL(sine2t[(p >> 12U) & 4095], g);

}

t_p[0] = p;

t_g[0] = g;

for (int h = 1; h < NBH; h++) {

uint32_t p = t_p[h];

int32_t g = t_g[h];

uint32_t dp = getDp(h);

for (int i = 0; i < BUFSIZE; i++) {

p += dp;

if (p > 0x00FFFFFF) {

p &= 0x00FFFFFF;

g = getGain(h);

}

outlet_out[i] = ___SMMLA(sine2t[(p >> 12U) & 4095], g, outlet_out[i]);

}

t_p[h] = p;

t_g[h] = g;

}