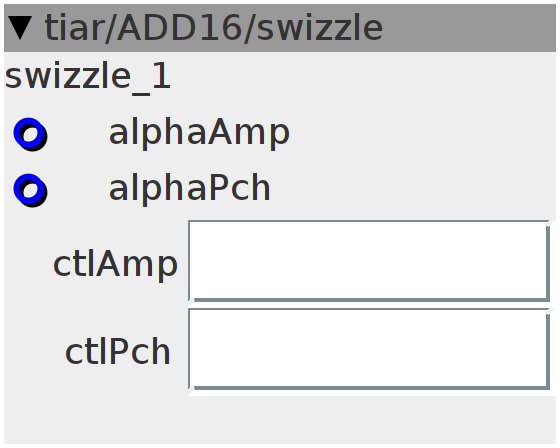

swizzle

Inlets

frac32 alphaAmp

frac32 alphaPch

Outlets

None

Attributes

objref ctlAmp

objref ctlPch

Declaration

static const uint32_t NBH = 16;

// 0, 1, 2, 3, 4, 5, 6, 7, 8, 9,10,11,12,13,14,15

const int dest[NBH] = {1, 0, 3, 2, 6, 8, 15, 9, 10, 13, 14, 4, 7, 12, 11, 5};

int32_t alphaAmp, alphaPch;

uint32_t getDp(int h) {

uint32_t dp0 = attr_ctlPch.getDp(h);

uint32_t dp1 = attr_ctlPch.getDp(dest[h]);

return ___SMMLA(alphaPch, dp1 - dp0, dp0 >> 5) << 5;

}

uint32_t getGain(int h) {

uint32_t g0 = attr_ctlAmp.getGain(h);

uint32_t g1 = attr_ctlAmp.getGain(dest[h]);

return ___SMMLA(alphaAmp, g1 - g0, g0 >> 5) << 5;

}

Init

alphaAmp = alphaPch = 0;

Control Rate

// a2*(3-2*a) // sigmoid

// a2*(1.5-a)*2

alphaAmp = __USAT(inlet_alphaAmp, 27);

alphaAmp = ___SMMUL(___SMMUL(alphaAmp, alphaAmp) << 5, (3 << 26) - alphaAmp)

<< (1 + 5);

alphaPch = __USAT(inlet_alphaPch, 27);

alphaPch = ___SMMUL(___SMMUL(alphaPch, alphaPch) << 5, (3 << 26) - alphaPch)

<< (1 + 5);