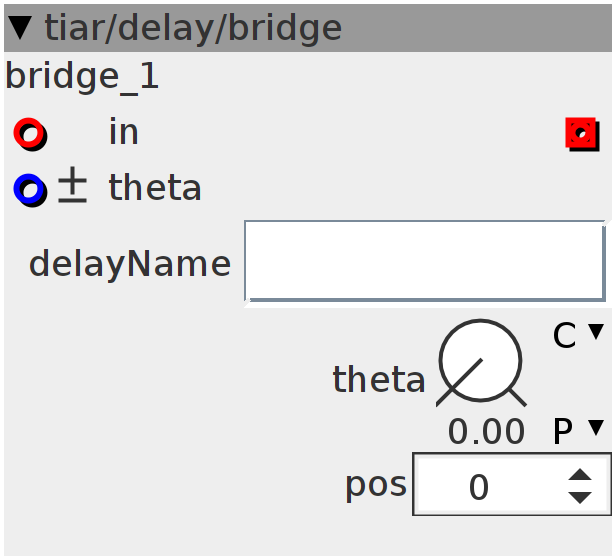

bridge

simple delay bridge with ins and outs delay coupling operator

Inlets

frac32buffer in

frac32.bipolar theta

Outlets

frac32buffer out

Parameters

frac32.u.map theta

int32 pos

Attributes

objref delayName

Declaration

void sinCos_q27(uint32_t theta, int32_t &c, int32_t &s) {

int32_t a = (theta & ((1 << 20) - 1)) << 8; // q28

uint32_t i = theta >> 20;

s = ___SMMLA(a, sine2t[i + 1] - sine2t[i], sine2t[i] >> 4);

i = (i + 1024) & 4095;

c = ___SMMLA(a, sine2t[i + 1] - sine2t[i], sine2t[i] >> 4);

}

Control Rate

int32_t c, s;

{

uint32_t theta = ((param_theta + inlet_theta) & 0x07FFFFFF) << 5;

sinCos_q27(theta, c, s);

}

// note: read/write indexes are set BUFSIZE samples back as we will process a

// batch of BUFSIZE samples so beware of overlappings when param_delays defer by

// less than 16 samples

int32_t a_rw = (attr_delayName.writepos - (BUFSIZE - 1) - param_pos) &

attr_delayName.LENGTHMASK;

// _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

for (int i = 0; i < BUFSIZE; i++) {

int32_t xA = attr_delayName.array[a_rw] << (27 - 15);

int32_t xB = inlet_in[i];

attr_delayName.array[a_rw] =

__SSAT(___SMMLS(xB, s, ___SMMUL(xA, c)) >> (22 - 15), 16);

a_rw = (a_rw + 1) & attr_delayName.LENGTHMASK;

outlet_out[i] = ___SMMLA(xB, c, ___SMMUL(xA, s)) << 5;

}