bridge

simple delay bridge without lowpass filters delay coupling operator

Inlets

frac32.bipolar theta

Outlets

None

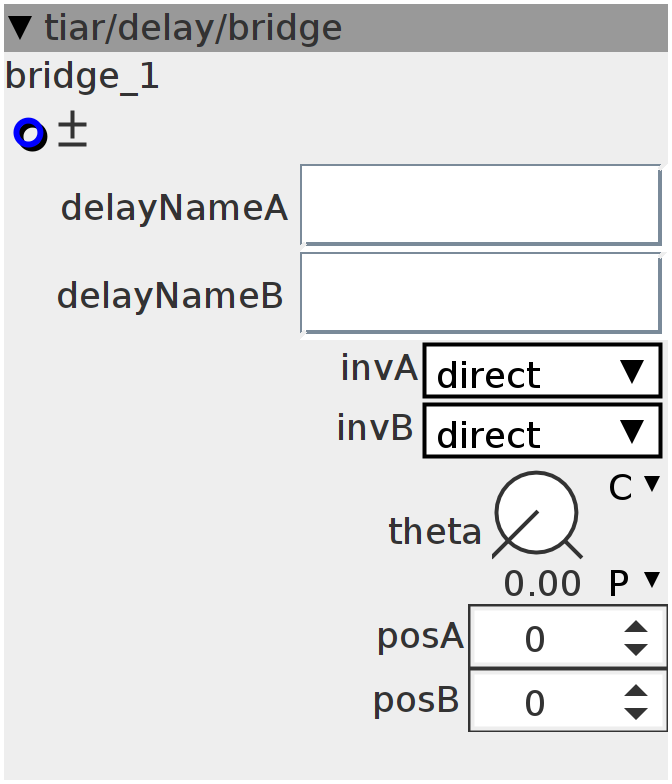

Parameters

frac32.u.map theta

int32 posA

int32 posB

Attributes

objref delayNameA

objref delayNameB

combo invA

combo invB

void sinCos_q27(uint32_t theta, int32_t &c, int32_t &s) {

int32_t a = (theta & ((1 << 20) - 1)) << 8; // q28

uint32_t i = theta >> 20;

s = ___SMMLA(a, sine2t[i + 1] - sine2t[i], sine2t[i] >> 4);

i = (i + 1024) & 4095;

c = ___SMMLA(a, sine2t[i + 1] - sine2t[i], sine2t[i] >> 4);

}

int32_t coefA = attr_invA ? 1 << 14 : -1 << 14;

int32_t coefB = attr_invB ? 1 << 14 : -1 << 14;int32_t c, s;

{

uint32_t theta = ((param_theta + inlet_theta) & 0x07FFFFFF) << 5;

sinCos_q27(theta, c, s);

}

// note: read/write indexes are set BUFSIZE samples back as we will process a

// batch of BUFSIZE samples so beware of overlappings when param_delays defer by

// less than 16 samples

int32_t a_rw = (attr_delayNameA.writepos - (BUFSIZE - 1) - param_posA) &

attr_delayNameA.LENGTHMASK;

int32_t b_rw = (attr_delayNameB.writepos - (BUFSIZE - 1) - param_posB) &

attr_delayNameB.LENGTHMASK;

// _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

for (int i = 0; i < BUFSIZE; i++) {

int32_t xA = attr_delayNameA.array[a_rw] << 14;

int32_t xB = attr_delayNameB.array[b_rw] << 14;

attr_delayNameA.array[a_rw] =

__SSAT(___SMMLS(xB, s, ___SMMUL(xA, c)) >> (24 - 15), 16);

a_rw = (a_rw + 1) & attr_delayNameA.LENGTHMASK;

attr_delayNameB.array[b_rw] =

__SSAT(___SMMLA(xB, c, ___SMMUL(xA, s)) >> (24 - 15), 16);

b_rw = (b_rw + 1) & attr_delayNameB.LENGTHMASK;

}