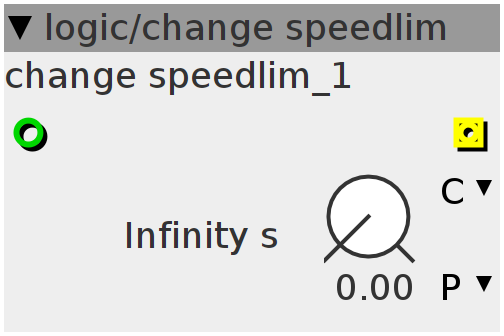

change speedlim

Generates a trigger pulse when current input value is different from previous value, with a minimum time interval between pulses.

IO Variants: 2

Variant: 1

Inlets

int32 in

Outlets

bool32 trigger pulse

Parameters

frac32.u.map.klineartime.reverse d

Declaration

int ptrig;

int32_t pval;

Init

ptrig = 0;

pval = 0;

Control Rate

if ((pval != inlet_in) & (!ptrig)) {

outlet_trig = 1;

pval = inlet_in;

ptrig = 1 << 27;

} else {

if (ptrig > 0) {

ptrig -= param_d >> 7;

} else

ptrig = 0;

outlet_trig = 0;

}Variant: 2

Inlets

frac32 in

Outlets

bool32 trigger pulse

Parameters

frac32.u.map.klineartime.reverse d

Declaration

int ptrig;

int32_t pval;

Init

ptrig = 0;

pval = 0;

Control Rate

if ((pval != inlet_in) & (!ptrig)) {

outlet_trig = 1;

pval = inlet_in;

ptrig = 1 << 27;

} else {

if (ptrig > 0) {

ptrig -= param_d >> 7;

} else

ptrig = 0;

outlet_trig = 0;

}