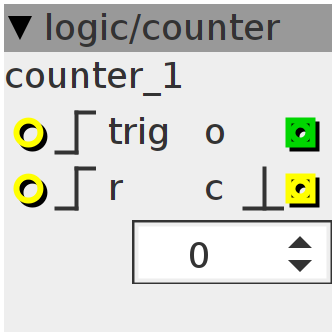

counter

cyclic up counter

Inlets

bool32.rising trigger

bool32.rising reset

Outlets

bool32.pulse carry pulse

int32 output

Parameters

int32 maximum

Declaration

int ntrig;

int rtrig;

int count;

Init

count = 0;

ntrig = 0;

rtrig = 0;

Control Rate

outlet_c = 0;

if ((inlet_trig > 0) && !ntrig) {

count += 1;

if (count >= param_maximum) {

count = 0;

outlet_c = 1;

}

ntrig = 1;

} else if (!(inlet_trig > 0))

ntrig = 0;

if ((inlet_r > 0) && !rtrig) {

count = 0;

rtrig = 1;

} else if (!(inlet_r > 0))

rtrig = 0;

outlet_o = count;